### UNIVERSITY OF CALIFORNIA, SAN DIEGO

### Design and Architecture of Automatically-generated Energy-reducing Coprocessors

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

John Morgan Sampson

Committee in charge:

Professor Steven Swanson, Co-Chair Professor Michael Taylor, Co-Chair Professor James Buckwalter Professor Lawrence Larson Professor Dean Tullsen

2010

Copyright John Morgan Sampson, 2010 All rights reserved. The dissertation of John Morgan Sampson is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Co-Chair

Co-Chair

University of California, San Diego

2010

### DEDICATION

To all those willing to wait for the fruits of their labor.

### EPIGRAPH

When the facts change, I change my mind. What do you do, sir? —John Maynard Keynes

## TABLE OF CONTENTS

|           | 3.6.2 Simulation infrastructure                                                                       | 32 |

|-----------|-------------------------------------------------------------------------------------------------------|----|

|           | 3.6.3 Synthesis                                                                                       | 32 |

|           |                                                                                                       | 34 |

|           | 3.7 Results                                                                                           | 34 |

|           | 3.7.1 Methodology                                                                                     | 35 |

|           |                                                                                                       | 35 |

|           | 3.7.3 System Efficiency                                                                               | 39 |

|           |                                                                                                       | 41 |

| Chapter 4 | From Conservation to Acceleration                                                                     | 43 |

| 1         |                                                                                                       | 44 |

|           |                                                                                                       | 47 |

|           | · -                                                                                                   | 48 |

|           | • -                                                                                                   | 49 |

|           | 4.2 Evaluating pipesplitting                                                                          | 50 |

|           | 4.2.1 Methodology                                                                                     | 50 |

|           | 4.2.2 ICC performance and EDP                                                                         | 54 |

|           | 4.3 Summary                                                                                           | 55 |

|           |                                                                                                       |    |

| Chapter 5 |                                                                                                       | 57 |

|           |                                                                                                       | 59 |

|           |                                                                                                       | 60 |

|           |                                                                                                       | 61 |

|           |                                                                                                       | 61 |

|           |                                                                                                       | 62 |

|           | 0.                                                                                                    | 62 |

|           | 0                                                                                                     | 63 |

|           | 5.5 Summary $\ldots$ | 65 |

| Chapter 6 | Conservation Core Structure and Scheduling                                                            | 67 |

|           | 6.1 Scheduling for C-Cores                                                                            | 67 |

|           | 6.1.1 Alignment                                                                                       | 71 |

|           | 6.1.2 Rescheduling for cachelets                                                                      | 71 |

|           | 6.2 Analysis                                                                                          | 73 |

|           | 6.2.1 Memory and parallelism                                                                          | 75 |

|           | 6.3 Future work                                                                                       | 77 |

|           | 6.3.1 Unrolling                                                                                       | 77 |

|           | $6.3.2$ Waves $\ldots$                                                                                | 78 |

|           | 6.3.3 Speculation                                                                                     | 79 |

|           | 6.4 Summary                                                                                           | 80 |

|           |                                                                                                       |    |

| Chapter 7    | Related Work                                   |

|--------------|------------------------------------------------|

|              | 7.1 Hardware specialization                    |

|              | 7.2 Heterogeneous systems                      |

|              | 7.3 Automatically generated hardware           |

|              | 7.4 Techniques                                 |

|              | 7.4.1 Bit-level parallelism                    |

|              | 7.4.2 Cache specialization                     |

|              | 7.4.3 Clock gating $\ldots$ 89                 |

|              | 7.4.4 Dynamic voltage and frequency scaling 89 |

|              | 7.5 Summary                                    |

| Chapter 8    | Summary                                        |

| Bibliography |                                                |

### LIST OF FIGURES

| Figure 3.1: | The high-level structure of a C-Core-enabled system                  | 16 |

|-------------|----------------------------------------------------------------------|----|

| Figure 3.2: | Dynamic coverage for given static instruction counts                 | 19 |

| Figure 3.3: | The C-Core Life Cycle                                                | 20 |

| Figure 3.4: | Conservation core example                                            | 24 |

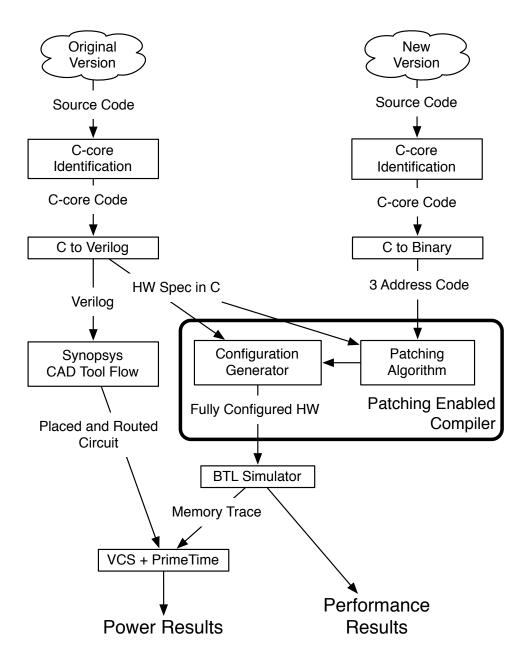

| Figure 3.5: | The C-Core C-to-hardware toolchain                                   | 31 |

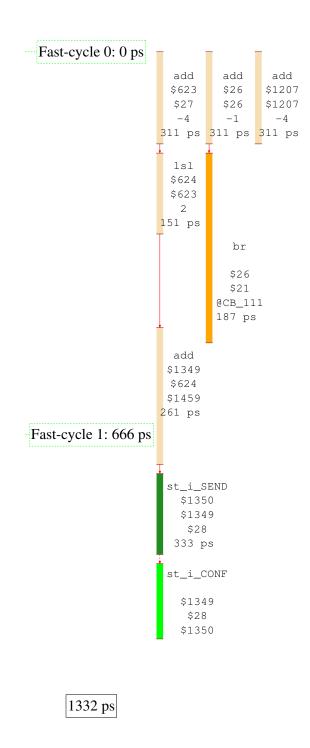

| Figure 3.6: | MCF 2006 conservation core for primal_bea_mpp() function             | 33 |

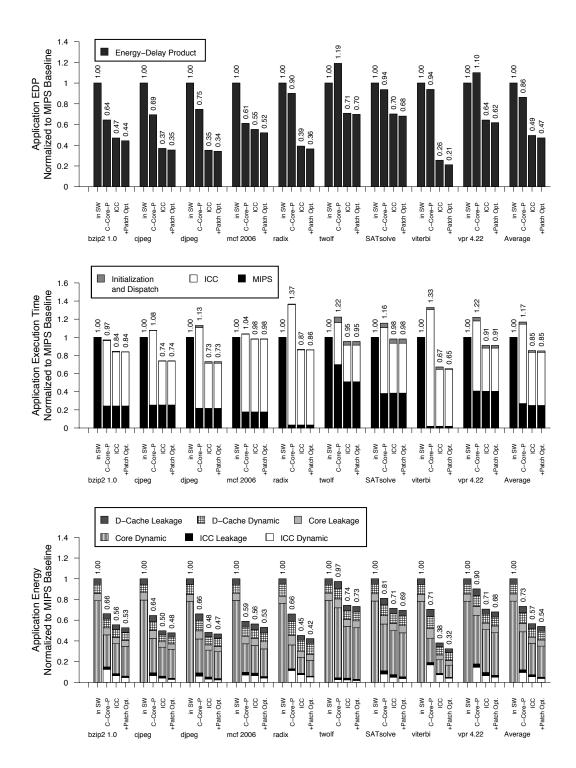

| Figure 3.7: | Conservation core energy efficiency                                  | 37 |

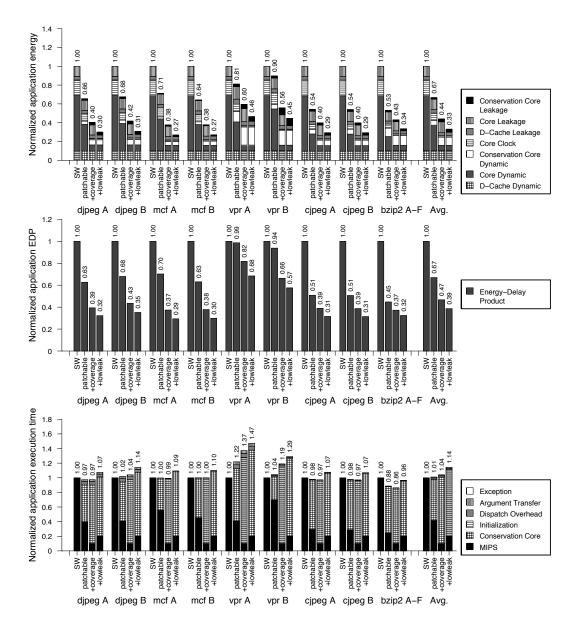

| Figure 3.8: | Full application system energy, EDP, and execution time for          |    |

|             | C-Cores, and projections for potential improvements                  | 38 |

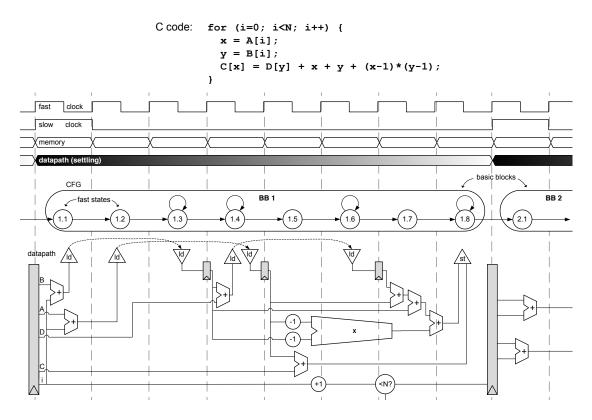

| Figure 4.1: | Example datapath and timing diagram demonstrating pipes-<br>plitting | 46 |

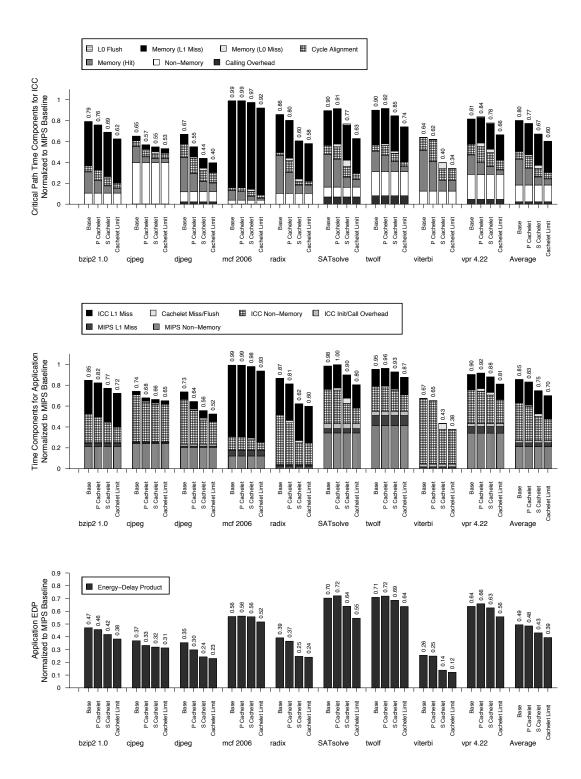

| Figure 4.2: |                                                                      | 52 |

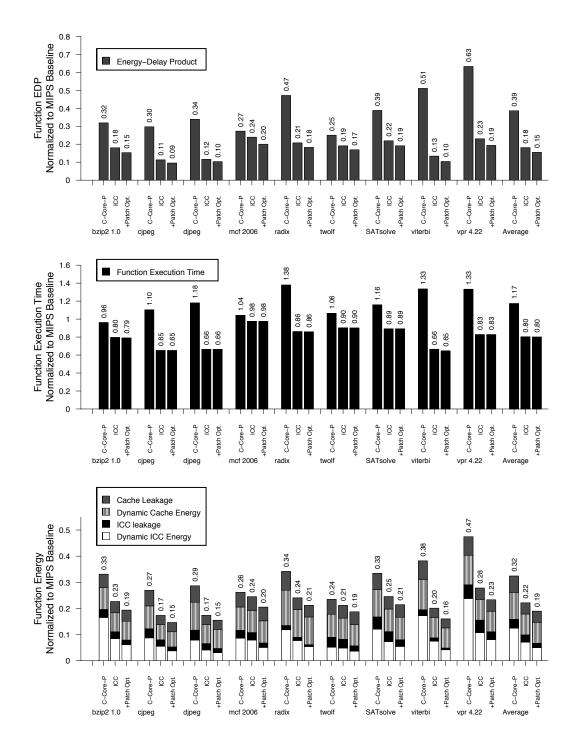

| Figure 4.3: | Application performance and efficiency with ICCs                     | 53 |

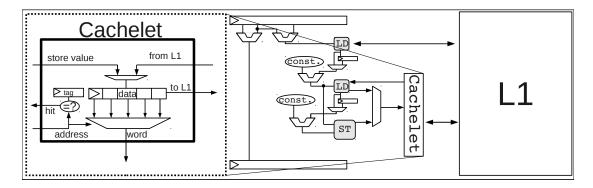

| Figure 5.1: | Cachelet architecture                                                | 59 |

| Figure 5.2: | Cachelet performance and efficiency                                  | 64 |

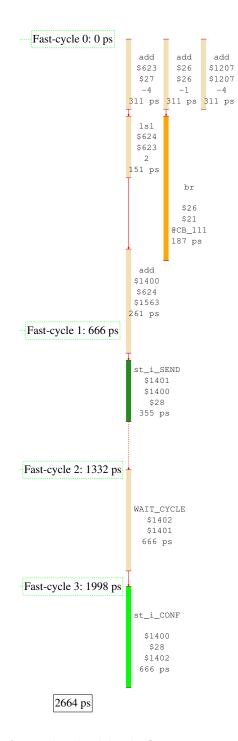

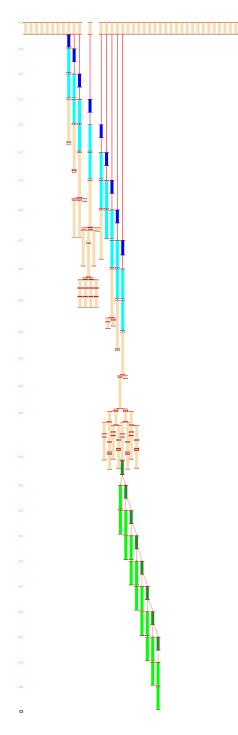

| Figure 6.1: | Schedule for a basic block                                           | 70 |

| Figure 6.2: | Schedule for a basic block with cachelets                            | 72 |

| Figure 6.3: | Schedule for a memory-constrained block                              | 76 |

### LIST OF TABLES

|            | The utilization wall                   |    |

|------------|----------------------------------------|----|

| Table 3.1: | Conservation core prototype statistics | 36 |

| Table 4.1: | ICC Workloads                          | 51 |

| Table 6.1: | Properties of ICC schedules            | 74 |

#### ACKNOWLEDGEMENTS

Many people have contributed directly and indirectly to my progress along the journey that lead me to construct this document. They are too many to name, and any attempt to impose a strict ordering on their contributions would be a fool's errand. I wish to thank those at UC Berkeley, UC San Diego, and at HP labs, my advisors, my colleagues, my family, my significant others, all those who let me kvetch incessantly, and all those who ever let me cook for them. You are all a part of my journey, and you are all appreciated.

Chapters 1, 2, 3, 7, and 8 contain material from "Conservation cores: reducing the energy of mature computations", by Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson and Michael Bedford Taylor, which appears in ASPLOS '10: Proceedings of the fifteenth edition of ASPLOS on Architectural support for programming languages and operating systems. The dissertation author was the secondary investigator and author of this paper. The material in Chapter 1 is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapters 1, 4, 5, 6, 7, and 8 contain material from "Energy-Delay Optimized Accelerators for Irregular Code", by Jack Sampson, Ganesh Venkatesh, Nathan Goulding, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor, which has been submitted for possible publication by IEEE in *Proceedings of* the 17th IEEE International Symposium on High Performance Computer Architecture (HPCA). The dissertation author was the primary investigator and author of this paper.

#### VITA AND PUBLICATIONS

| 2000-2003 | Teaching assistant<br>University of California, Berkeley                                   |

|-----------|--------------------------------------------------------------------------------------------|

| 2002      | B. S. in Electrical Engineering and Computer Science<br>University of California, Berkeley |

| 2003-2010 | Research assistant<br>University of California, San Diego                                  |

| 2005      | Internship<br>HP Labs<br>Palo Alto, California                                             |

| 2006      | Internship<br>HP Labs<br>Palo Alto, California                                             |

| 2008      | C. Phil. in Computer Engineering<br>University of California, San Diego                    |

| 2010      | Ph. D. in Computer Engineering<br>University of California, San Diego                      |

#### PUBLICATIONS

Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson, Michael Bedford Taylor, "Conservation Cores: Reducing the Energy of Mature Computations", *Proceedings of* the Fifteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), March 2010.

Jack Sampson, Ruben Gonzalez, Jean-Francois Collard, Norm Jouppi, Mike Schlansker and Brad Calder, "Exploiting Fine-Grained Data Parallelism with Chip Multiprocessors and Fast Barriers", *Proceedings of the 39th International Sympo*sium on Microarchitecture (MICRO), December 2006.

Christophe Lemuet, Jack Sampson, Jean-Francois Collard, Norm Jouppi, "The Potential Energy Efficiency of Vector Acceleration", *Proceedings of the 2006 ACM* / *IEEE conference on Supercomputing (SC)*, November 2006

Weihaw Chuang, Satish Narayanasamy, Ganesh Venkatesh, Jack Sampson, Michael Van Biesbrouck, Gilles Pokam, Osvaldo Colavin, Brad Calder, "Unbounded Page-Based Transactional Memory", Proceedings of the Thirteenth International Conference on Architectural Support for Programming Languages and Operating Systems, October 2006 Erez Perelman, Marzia Polito, Jean-Yves Bouguet, John Sampson, Brad Calder, Carole Dulong, "Detecting Phases in Parallel Applications on Shared Memory Architectures", *Proceedings of the 20th IEEE International Parallel and Distributed Processing Symposium*, April 2006

Lieven Eeckhout, John Sampson, and Brad Calder, "Exploiting Program Microarchitecture Independent Characteristics and Phase Behavior for Reduced Benchmark Suite Simulation", *In Proceedings of the 2005 IEEE International Symposium* on Workload Characterization, October 2005

Jeremy Lau, Jack Sampson, Erez Perelman, Greg Hamerly, Brad Calder, "The Strong Correlation Between Code Signatures and Performance", *Proceedings of the 5th International Symposium on Performance Analysis of Systems and Software*, March 2005

#### ABSTRACT OF THE DISSERTATION

### Design and Architecture of Automatically-generated Energy-reducing Coprocessors

by

John Morgan Sampson

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2010

Professor Steven Swanson, Co-Chair Professor Michael Taylor, Co-Chair

For many years, improvements to CMOS process technologies fueled rapid growth in processor performance and throughput. Each process generation brought exponentially more transistors and exponentially reduced the per-transistor switching power. However, concerns over leakage currents have moved us out of the classical CMOS scaling regime. Although the number of available transistors continues to rise, their switching power no longer declines. In contrast to transistor counts, power budgets remain fixed due to limitations on cooling or battery life. Thus, with each new process generation, an exponentially decreasing fraction of the available transistors can be simultaneously switched. The growing divide between available transistors and utilizable transistors leads to a *utilization wall*.

This dissertation characterizes the utilization wall and proposes *conserva*tion cores as a means of surmounting its most pressing challenges. Conservation cores, or *C-Cores*, are application-specific hardware circuits created to reduce energy consumption on computationally-intensive applications with complex control logic and irregular memory access patterns. C-Cores are drop-in replacements for existing source code, and make use of limited reconfigurability to adapt to software changes over time. The design and implementation of these specialized execution engines pose challenges with respect to code selection, automatic synthesis, choice of programming model, longevity/robustness, and system integration.

This dissertation addresses many of these challenges through the development of an automated conservation core toolchain. The toolchain automatically extracts the key kernels from a target workload and uses a custom C-to-silicon infrastructure to generate 45 nm implementations of the C-Cores. C-Cores employ a new pipeline design technique called *pipeline splitting*, or *pipesplitting*. This technique reduces clock power, increases memory parallelism, and further exploits operation-level parallelism. C-Cores also incorporate specialized energy-efficient per-instruction data caches called *cachelets* into the datapath, which allow for sub-cycle cache-coherent memory accesses.

An evaluation of C-Cores against an efficient in-order processor shows that C-Cores speed up the code they target by  $1.5\times$ , improve EDP by  $6.9\times$  and accelerate the whole application by  $1.33\times$  on average, while reducing application energy-delay by 57%.

# Chapter 1

# Introduction

For many years, improvements to CMOS process technologies fueled rapid growth in processor performance and throughput. Each process generation brought exponentially more transistors and exponentially reduced the per-transistor switching power. With these ample and efficient resources, computer architects were able to increase the number of cores per processor and employ increasingly sophisticated mechanisms to improve the performance of each core.

In recent years, however, the benefits of newer process generations have changed. Although the number of available transistors continues to rise, their switching power no longer declines. Concerns over leakage currents have moved us out of the classical CMOS scaling regime. We cannot employ the additional transistors from newer process generations if their use violates the power budget: Pragmatic concerns, such as thermal management, cost of ownership, and battery life, hold power budgets fixed. Thus, with each process generation, an exponentially decreasing fraction of the available transistors can be simultaneously switched. We term this growing divide between available transistors and utilizable transistors the *utilization wall*. The homogeneous multi-core approach to designing processors is ill-suited to face this challenge. However, the leakage-limited scaling regime introduces a new landscape in which heterogeneous designs with specialized hardware hold significant promise.

Faced with the utilization wall, designers find each new process generation leaves them with undesirable choices. They could allow the area budget to scale down with power, but that would signal the end of exponentially increasing circuit integration. As this increasing integration, commonly known as Moore's Law, has powered the past several decades of architectural innovation, this is not an acceptable option. For a fixed area budget, either some of that area must lay fallow at any given time, *dark silicon*, or the area must contain underutilized transistors, *dim silicon*. Such underutilization is most commonly accomplished via underclocking, which limits performance. Heterogeneous designs offer a means to exploit dark silicon: Only cores that are well matched to the current set of computations are active, and all others remain dark. As the current set of computations changes, cores can move between active and dark status, running threads on the most closely matching silicon.

Specialization and heterogeneity are appealing from both power and performance perspectives, and both are challenging from a system perspective. Producing a sufficient diversity of specialized hardware to provide high coverage for a non-trivial target workload requires significant design automation. Likewise, the hardware produced must reduce energy for serial and irregular code, as well as parallel code, or the technique will be of limited applicability. Custom ASICs and accelerators for highly parallel computations are well studied, but many open questions remain for the systematic generation of hardware for irregular code regions.

This dissertation characterizes the utilization wall and proposes *conservation cores* as a means of addressing the challenges of dark silicon. Conservation cores, or *C-Cores*, are application-specific hardware circuits created for the purpose of reducing energy consumption on computationally intensive applications with irregular code bases. C-Cores improve the energy efficiency of irregular codes by converting dark silicon into a collection of energy-saving, application-specialized cores. Each C-Core is a drop-in replacement for a region of code in the source application. These cores are produced by an automated toolchain which transforms regions of C source into C-Cores and transparently modifies the original applications to use the C-Cores. C-Cores, unlike many other approaches, can target nearly arbitrary code regions.

Conservation cores have a different goal than conventional application-

specific circuits, and we differentiate between C-Cores and the more common *accelerators* along several axes. Accelerators focus on improving performance, at a potentially worse, equal, or better energy efficiency. As their name suggests, designers rarely deploy accelerators for code where performance does not greatly benefit from customized hardware. Conservation cores, on the other hand, focus on energy reduction. Serial and irregular codes are valid targets for energy reduction via conservation cores, even if performance benefits are limited. Conservation cores aim to always reduce energy consumption and to accelerate where practical. Conservation cores that are also accelerators are possible: Chapters 4 and 5 explore techniques for improving the performance of C-Cores while maintaining energy efficiency.

Even if, for a given C-Core, the hardware specialization that provides energy efficiency does not translate into better performance, energy efficiency can translate directly to better throughput. Under the utilization wall, such specialized, energyefficient processors can increase parallelism by reducing the per-computation power requirements and allowing more computations to execute under the same power budget. Therefore, while single-threaded performance is important, especially for difficult to parallelize irregular code bases, performance should not be purchased at the expense of forsaking energy efficiency.

Shifting the focus from performance-at-all-costs to efficiency allows C-Cores to target a broader range of applications than accelerators. C-Cores, unlike most accelerators, can target both parallel and serial portions of an application. Accelerators provide benefits for codes with large amounts of parallelism and predictable communication patterns, as these codes map naturally onto hardware. Thus, parallelism-intensive regions of code that are hot (i.e., occupy a high percentage of running time) are the best candidates for implementation as accelerators. On the other hand, C-Cores are parallelism-agnostic: Hot code with a tight critical path, little parallelism, and/or very poor memory behavior is an excellent candidate for a C-Core: C-Cores can greatly reduce the number of transistor toggles required to execute that code, saving energy. For instance, our results show that C-Cores can deliver significant energy savings for irregular, integer applications

(e.g., MCF from SPEC 2006) that would be difficult to automatically accelerate with specialized hardware.

Over the course of this dissertation, we will examine the utilization wall, conservation cores, and how these conservation cores rise to the challenges of a leakage limited scaling regime. Chapter 2 examines the origins and implications of the utilization wall. We discuss the theory behind classical and leakage limited CMOS scaling, and present our own empirical results for the utilization wall. We then discuss how the unique challenges of the utilization wall lead us to develop the C-Core approach.

Chapter 3 describes the system architecture for C-Core enabled systems, our toolchain for automatically creating and compiling for C-Cores, and presents and evaluates a prototype C-Core architecture. The toolchain automatically extracts the key kernels from a target workload and uses a custom C-to-silicon infrastructure to generate 45 nm implementations of the C-Cores. It also automates the process of evaluating and compiling for C-Core enabled systems. We use this toolchain to produce and evaluate a set of prototype C-Cores from multiple versions of several applications. We show that our prototype C-Cores provide significant energy and energy-delay savings over an efficient, in-order MIPS processor.

Chapters 4 and 5 describe enhancements to C-Core performance and energy efficiency. Our prototype C-Cores offer substantial energy savings, but have room to improve on performance and energy efficiency in three key areas: Memory ordering enforcement, reconfiguration mechanisms, and load-use latency all benefit from targeted optimizations. To improve C-Core performance we employ a new pipeline design technique called *pipeline splitting*, or *pipesplitting*. This technique reduces clock power, increases memory parallelism, and further exploits ILP. To reduce the energy, area, and operator delay costs incurred by the software adaptation mechanisms from [VSG<sup>+</sup>10] we exploit a more nuanced form of reconfiguration. We also explore incorporating specialized energy-efficient per-instruction data caches called *cachelets*, which allow for sub-cycle cache-coherent memory accesses. The first two of these advances are presented in Chapter 4, and the third is the focus of Chapter 5. Chapter 6 analyzes the hardware produced by our automated toolchain, and explores the impact and challenges of scheduling operations on C-Cores. We discuss why operation scheduling is important for C-Cores and why traditional modulo scheduling techniques are not applicable. We examine the limitations of a block-based execution and scheduling model in the face of small basic blocks, and highlight possible avenues for improving block size and exposed parallelism.

Chapter 7 surveys other approaches to energy reduction, accelerator architectures, and automated hardware generation. It also discusses differences in technique from related work for our implementations of scheduling, caching, and other components of our approach. Through these comparisons, we place conservation cores in the context of broader efforts in hardware specialization and highlight novel aspects of the C-Core approach.

Finally, in Chapter 8 we summarize the contributions of this dissertation, including the introduction of the utilization wall and the design and evaluation of C-Cores and C-Core enhancing techniques.

### Acknowledgments

Portions of this research were funded by the US National Science Foundation under NSF CAREER Awards 06483880 and 0846152, and under NSF CCF Award 0811794.

This chapter contains material from "Conservation cores: reducing the energy of mature computations", by Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson and Michael Bedford Taylor, which appears in *ASPLOS '10: Proceedings of the fifteenth edition of ASPLOS on Architectural support for programming languages and operating systems.* The dissertation author was the secondary investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or

commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

This chapter contains material from "Energy-Delay Optimized Accelerators for Irregular Code", by Jack Sampson, Ganesh Venkatesh, Nathan Goulding, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor, which has been submitted for possible publication by IEEE in *Proceedings of the 17th IEEE International Symposium on High Performance Computer Architecture (HPCA)*. The dissertation author was the primary investigator and author of this paper.

# Chapter 2

# The Utilization Wall

In this chapter, we examine the nature of the utilization wall in detail, and motivate heterogeneous multiprocessors with application specialized cores as a means of dealing with its consequences. We show how scaling theory predicts that the transition from classical to leakage-limited regime will lead to the utilization wall. We then demonstrate how these theoretical models predict current practice, confirming the exponential nature of the utilization wall. Finally, we discuss how heterogeneous multi-core processors address the challenges posed by utilization wall in ways that homogeneous multi-core processors do not.

# 2.1 The Utilization Wall

In this section we provide the theoretical background for the utilization wall and then provide evidence of how it is already affecting designs. We show that scaling theory predicts the utilization wall to be an exponentially worsening problem. We then lend support to this prediction with our own experiments at 90 and 45 nm process nodes.

### 2.1.1 Theory

The utilization wall arises because of a breakdown of the classical CMOS scaling described by Dennard [DGR<sup>+</sup>74] in his 1974 paper. The "Classical Scaling"

column in Table 2.1 shows the key elements of the classical CMOS scaling model. Associated with each transition between CMOS processes is a geometry scaling factor S, typically 1.4×. Classical CMOS scaling holds that transistor capacitances decrease roughly by this factor of S with each process shrink. At the same time, transistor switching frequency rises by S and the number of transistors on the die increases by  $S^2$ . Until recently, it has been possible to scale supply voltage by 1/S, leading to constant power consumption for a fixed-size chip running at full frequency. Scaling the supply voltage requires that we also scale the threshold voltage proportionally if we wish to maintain switching frequency. Historically, this was not an issue because leakage, although increasing exponentially, was not significant in process nodes above 130 nm.

In the current process scaling regime, transistor densities and speeds continue to increase with Moore's Law. Unfortunately, to curtail leakage currents, limits on threshold voltage scaling now prevent supply voltage scaling. As a result, full chip, full frequency power is now rising as  $S^2$ . The introduction of 3D CMOS technology will exacerbate this trend further. Table 2.1 summarizes these trends. The equations in the "Classical Scaling" column governed scaling up until 130 nm. The equations in the "Leakage Limited" column govern scaling at 90 nm and below.

### 2.1.2 Practice

The result of these trends is a technology-imposed *utilization wall* that limits the fraction of the chip we can use at full speed at one time. The effects of the utilization wall are already indirectly apparent in modern processors: Intel's Nehalem provides a "turbo mode" that powers off some cores in order to run others at higher speeds. Another strong indication is the divergence between native transistor switching speeds and processor frequencies. Although the former have continued to double every two process generations, the latter have not increased substantially over the last 5 years.

To quantify the current impact of the utilization wall, we synthesized, placed, and routed several circuits using the Synopsys Design and IC Compilers.

Table 2.1: The utilization wall The utilization wall is a consequence of CMOS scaling theory and current-day technology constraints, assuming fixed power and chip area. The Classical Scaling column assumes that designers can lower  $V_t$  arbitrarily. In the Leakage Limited case, constraints on  $V_t$ , necessary to prevent unmanageable leakage currents, hinder scaling and create the utilization wall.

| Param.     | Description                       | Relation                         | Classical      | Leakage        |

|------------|-----------------------------------|----------------------------------|----------------|----------------|

| Param.     |                                   |                                  | Scaling        | Limited        |

| В          | power budget                      |                                  | 1              | 1              |

| А          | chip size                         |                                  | 1              | 1              |

| $V_t$      | threshold voltage                 |                                  | 1/S            | 1              |

| $V_{dd}$   | supply voltage                    | $\sim V_t \times 3$              | 1/S            | 1              |

| $t_{ox}$   | oxide thickness                   |                                  | 1/S            | 1/S            |

| W, L       | transistor dimensions             |                                  | 1/S            | 1/S            |

| Isat       | saturation current                | $WV_{dd}/t_{ox}$                 | 1/S            | 1              |

| p          | device power<br>at full frequency | $I_{sat}V_{dd}$                  | $1/S^{2}$      | 1              |

| $C_{gate}$ | capacitance                       | $WL/t_{ox}$                      | 1/S            | 1/S            |

| F          | device frequency                  | $\frac{I_{sat}}{C_{gate}V_{dd}}$ | $\mathbf{S}$   | $\mathbf{S}$   |

| D          | devices per chip                  | A/(WL)                           | $\mathbf{S}^2$ | $\mathbf{S}^2$ |

| Р          | full die, full                    | $D \times p$                     | 1              | $S^2$          |

|            | frequency power                   |                                  |                | 2              |

| U          | utilization at                    | B/P                              | 1              | $1/S^2$        |

|            | fixed power                       |                                  |                | -, 0           |

Table 2.2: Experiments quantifying the utilization wall We use Synopsys CAD tools and TSMC standard cell libraries to evaluate the power and utilization of a  $300 \text{ mm}^2$  chip filled with 64-bit adders, separated by registers. We use these operators to approximate active logic in a processor.

| Process             | 90 nm TSMC | 45  nm TSMC | 32 nm ITRS |

|---------------------|------------|-------------|------------|

| Frequency (GHz)     | 2.1        | 5.2         | 7.3        |

| $mm^2$ Per Op.      | .00724     | .00164      | .00082     |

| # Operators         | 41k        | 180k        | 360k       |

| Full Chip Watts     | 455        | 1225        | 2401       |

| Utilization at 80 W | 17.6%      | 6.5%        | 3.3%       |

Table 2.2 summarizes our findings. For each process, we used the corresponding TSMC standard cell libraries to evaluate power and area. We filled a 300 mm<sup>2</sup> chip with 64-bit operators to approximate active logic on a microprocessor die. Each operator is a 64-bit adder with registered inputs and outputs, which runs at its maximum frequency in that process. In a 90 nm TSMC process, running a chip at full frequency would require 455 W. This means that only 17.6% of the chip could be simultaneously active in an 80 W budget. In a 45 nm TSMC process, a similar design would require 1225 W, resulting in just 6.5% utilization at 80 W. This shows a reduction of 2.6× attributable to the utilization wall. The equations in Table 2.1 predicted a larger, 4× reduction. The difference is due to process and standard cell tweaks implemented between the 90 nm and 45 nm generations.

### 2.2 Implications of the Utilization Wall

Table 2.2 also extrapolates to 32 nm based on ITRS data for 45 and 32 nm processes. ITRS roadmap projections and CMOS scaling theory suggest that this percentage will decrease to less than 3.5% in 32 nm, and will continue to decrease by almost half with each process generation. Thus, the utilization wall is getting exponentially worse, roughly by a factor of two, with each process generation.

The remainder of the transistor budget must be either left unused, leaving dark silicon, or purchased at the expense of underutilizing all transistors in the design. The latter renders the whole processor dim silicon. For scaling existing multi-core processor designs, designers have choices that span a variety of design points. However, the best they can do is exploit the factor of S (e.g.,  $1.4\times$ ) reduction in transistor switching energy that each generation brings. Regardless of whether designers a) increase frequency by a factor of  $1.4\times$ , b) increase core count by  $1.4\times$ , c) increase core count by  $2\times$ , and reduce frequency by  $1.4\times$ , or d) some compromise of the three, the utilization wall ensures transistor speeds and densities are rapidly out-pacing the available power budget to switch them.

The situation is brighter for less conventional designs. Provided that only a subset of the transistors are active at the same time, designers can still harness all

of the available transistor budget at full speed. In a homogeneous design, turning off one compute unit in favor of an identical one offers few benefits. In contrast, for a heterogeneous design, there are clear benefits to turning off one compute unit in favor of turning on another that is more specialized for the current task.

# 2.3 Using Heterogeneity to Scale the Utilization Wall

Heterogeneity and specialization are effective responses to the utilization wall and the dark silicon problem. Increasingly, specialized processors offer large energy savings with little to no opportunity cost: The silicon area that they consume would otherwise go unused because of the utilization wall. Thus, specialized silicon can trade cheap area for valuable energy efficiency.

Specialization is especially profitable in extremely power-constrained designs. This includes the mobile application processors that power the world's emerging computing platforms, including cell phones, e-book readers, media players, and other portable devices. Mobile application processors differ from conventional laptop or desktop processors. They have vastly lower power budgets – often less than 375 mW – and usage is heavily concentrated around a core collection of applications. Mobile designs already tend to be heterogeneous platforms. Mobile designers reduce power consumption, in part, by leveraging customized low-power hardware implementations of common functions such as audio and video decoders and 3G/4G radio processing. These computations are highly parallel and exceptionally well-suited to traditional accelerator or custom ASIC implementations.

The remaining code (user interface elements, application logic, operating system, etc.) resembles traditional desktop code and is ill-suited to conventional, parallelism-centric accelerator architectures. This code has traditionally been of limited importance. However, the rising popularity of sophisticated mobile applications suggests this code will become more prominent and consume larger fractions of device power budgets. As a result, applying hardware specialization to frequently-executed irregular code regions will become a profitable system-level optimization. Likewise, the resemblance between these code regions and traditional desktop applications means that hardware beneficial to either should benefit both.

For parallel and highly regular regions of code, traditional accelerator approaches will continue to apply. Many already produce low-power hardware, or offer sufficient performance to trade performance for power. However, to address the challenges of the utilization wall, we must provide specialization for more than just those portions of code trivially mapped into hardware. Similarly, to be a scalable solution, we must be able to map new codes onto new or existing specialized hardware as workloads change and applications evolve. Our approach to addressing the utilization wall is the construction of a fully automated toolchain that produces specialized execution engines called conservation cores that act as drop-in replacements for existing code. In the next chapter, we will explore both the conservation core approach and the conservation core toolchain.

### Acknowledgments

Portions of this research were funded by the US National Science Foundation under NSF CAREER Awards 06483880 and 0846152, and under NSF CCF Award 0811794.

This chapter contains material from "Conservation cores: reducing the energy of mature computations", by Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson and Michael Bedford Taylor, which appears in *ASPLOS '10: Proceedings of the fifteenth edition of ASPLOS on Architectural support for programming languages and operating systems.* The dissertation author was the secondary investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for com-

ponents of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

This chapter contains material from "Energy-Delay Optimized Accelerators for Irregular Code", by Jack Sampson, Ganesh Venkatesh, Nathan Goulding, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor, which has been submitted for possible publication by IEEE in *Proceedings of the 43rd annual International Symposium on Microarchitecture (MICRO)*. The dissertation author was the primary investigator and author of this paper.

# Chapter 3

# The Design of Conservation Core Enabled Systems

In the previous chapter, we saw how growing transistor counts, limited power budgets, and the breakdown of voltage scaling conspire to create a utilization wall that limits the fraction of a chip that can run at full speed at one time. This leads to an increase in dark silicon with every process generation. Likewise, we saw indications that heterogeneous systems that can translate increasing transistor budgets into increasing levels of specialization may be able to exploit the dark silicon. Our approach to heterogeneous system design is built around automatically generated specialized processors that focus on reducing energy and energy-delay for code regions with irregular control flow and memory patterns. We call these processors conservation cores, or C-Cores,

Incorporating C-Cores into multi-processors, especially at a scale large enough to save power across many applications with multiple hot spots, raises a number of challenges:

- C-Core Selection In order to build C-Cores, we must be able to identify which pieces of code are the best candidates for conversion into C-Cores. The code should account for a significant portion of runtime and energy, and stem from a relatively stable code base.

- 2. Automatic synthesis Designing numerous C-Cores by hand is not scalable,

so it must be possible to synthesize C-Cores automatically and correctly, without significant human intervention.

- 3. **Programming model** It should not be necessary to rewrite applications to make use of C-Cores. The system must utilize them automatically.

- 4. Longevity Conservation cores should remain useful even as the code they are designed to replace evolves.

- 5. System integration Since C-Cores should work seamlessly with existing code, the C-Core hardware and memory model must be tightly integrated with the rest of system.

In this chapter, we develop the conservation core architecture and show how our design addresses programming model and system integration challenges. We present our vision for how C-Cores will be selected, created, integrated, used, and adapted to workload and application changes over time. We call this the C-Core's "life cycle," and present our toolchain which automates each of the stages in that life cycle. We describe our toolchain in detail and evaluate the prototype C-Cores that it produces. Subsequent chapters will focus on improving both the performance and energy efficiency of these initial prototype C-Cores.

### 3.1 Conservation cores: System overview

This section provides an overview, describing the composition of a prototypical C-Core system. Architectures based on specialized hardware must address three core issues: 1) how the specialized core maintains coherence with the host system, 2) how the specialized core integrates with more general processing resources to handle code that does not justify building specialized hardware, and 3) how the system withstands changes to the software that it targets. We address these three core questions in turn, discussing the sharing of our coherent L1, the movement of execution between CPU and C-Core, and our approach to handling target application program changes.

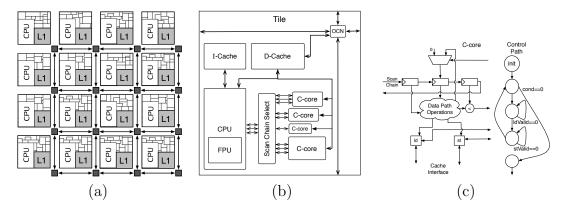

Figure 3.1: The high-level structure of a C-Core-enabled system A C-Core-enabled system (a) is made up of multiple individual tiles (b), each of which contains multiple C-Cores (c). Conservation cores communicate with the rest of the system through a coherent memory system and a simple scan-chain-based interface. Different tiles may contain different C-Cores. Not drawn to scale.

#### **3.1.1** Basic chip-level architecture

A C-Core-enabled system includes multiple C-Cores embedded in a multior many-core tiled array like the one in Figure 3.1(a). Each tile of the array contains a general purpose processor (the "CPU"), cache and interconnect resources, and a collection of tightly-coupled C-Cores. Collectively, the C-Cores and CPU share the tile's resources, including the coherent L1 data cache, the on-chip network interface, and FPU.

Within a tile (Figure 3.1(b)), the C-Cores interface to the host CPU via a direct, multiplexed connection to the L1 cache. They also connect directly to the host CPU through a collection of scan chains. These allow the CPU to read and write all state within the C-Cores. The CPU uses these scan chains for passing arguments, for context switching, and for patching the C-Cores. The scan chain interface is covered in more detail in section 3.3.2. These facilities allow the system to reconfigure a C-Core to run future and past modified versions of the source code that was used to generate the C-Cores. Most data transfer occurs through the coherent L1 cache connection.

A shared, coherent cache is an attractive option for conservation cores because of their focus on irregular code. With irregular accesses and control flows unsuited to modulo scheduling, C-Cores are sensitive to memory latency as well as bandwidth. Caching can greatly reduce average memory access time, especially for dependent loads. As C-Cores already target code with irregular control flows, the variability in memory access time doesn't add significant additional complexity.

By having C-Cores share the same path to memory as the processor, dropin semantics are easier to maintain. Likewise, C-Cores are trivially kept coherent with processor memory because the accesses go to the same cache. For applications with cache-friendly access patterns, caching also improves energy efficiency over directly accessing main memory.

### 3.1.2 Execution model

Each C-Core targets frequently executed, or hot, regions of an application. It achieves energy and power savings by creating specialized hardware datapaths that eliminate much of the overhead in conventional processor pipelines. Overheads reduced or removed include instruction fetch, register file accesses, and bypassing. These datapaths are controlled by a set of state machines that closely mirror the control flow graph of the source program. This mirroring allows for precise replication of the same semantics that the code would have if it were executing on the CPU. The shared, coherent L1 makes this as true for memory state as for control flow.

Portions of applications not important enough to be supported by C-Cores continue to run on the CPU. The CPU also serves as a fallback to support applications that were not available at the time of the manufacture of the chip. Similarly, exceptional behavior is supported with traps to the CPU. Execution shifts back and forth between the CPU and various C-Cores as an application enters and exits the code regions that C-Cores support.

#### 3.1.3 Future proofing

Although the C-Cores are created to support existing versions of specific applications, they also need to support newer versions that are released after the original C-Cores were synthesized. To do this, we implement all three reconfiguration mechanisms described in [VSG<sup>+</sup>10]. The C-Cores include reconfiguration bits which allow the behavior of C-Cores to adapt to commonly found changes in programs. Small changes, such as replacing one constant value in a program with another, are handled within the C-Core via reconfiguration. Larger changes are handled by forcing traps to software on certain CFG edges. Section 3.4 briefly discusses how the patching process fits into our automated toolchain and how these reconfiguration bits are configured. However, the details of the patching algorithms are outside the scope of this dissertation and can be found in [VSG<sup>+</sup>10].

### 3.2 The C-Core Life Cycle

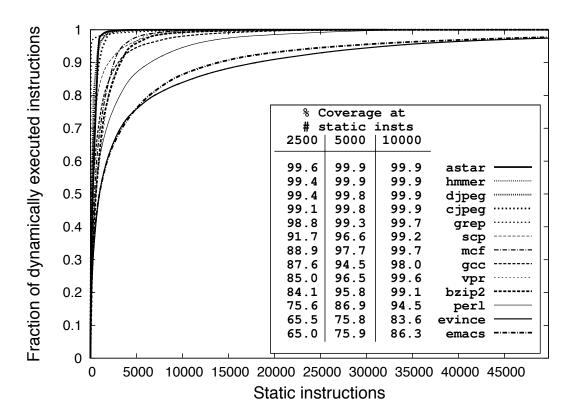

For the C-Core approach to be successful, we must be able to map most execution onto C-Cores. Furthermore, for C-Cores to achieve high coverage in a reasonable amount of area, a relatively small fraction of the application's static instructions must account for a large fraction of execution. Fortunately, this is true for many programs. Figure 3.2 shows the fraction of dynamically executed x86 instructions (y-axis) covered by the number of static x86 instructions (x-axis) for a broad-ranging set of applications. These applications include SPECCPU2006 integer benchmarks astar and hmmer, desktop applications evince, emacs, grep, gcc, perl, and scp, and five applications for which we will construct C-Cores prototypes in this chapter. For many applications, the curve is quite steep. This means that converting a relatively small number of static instructions into hardware will cover a very large fraction of execution.

The C-Core approach must be scalable in design effort as well as area. We will address this through automation. As workloads change, new applications and new versions of applications can be run through our automated toolchain. Dropin semantics allow the specialized hardware to be used transparently, without manual code changes. While this approach imposes some constraints on potential optimizations, especially on the memory system, it makes the conservation core approach scalable in effort.

Figure 3.2: **Dynamic coverage for given static instruction counts** We show the cumulative distribution of dynamic coverage (on the vertical axis) as a function of the number of static instructions executed. For many x86 programs profiled, a small number of static instructions cover much of dynamic execution. This implies that a small amount of specialized hardware could cover large portions of execution for each of these programs.

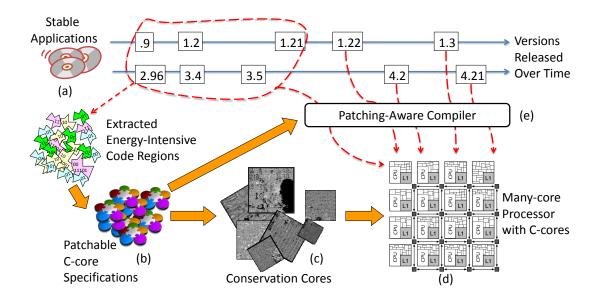

Figure 3.3: The C-Core Life Cycle A profiler (a) extracts a set of energyintensive code regions from a corpus of stable applications in the processor's target domain. The toolchain generalizes these regions into patchable C-Core specifications (b), translates them into circuits via an automated synthesis infrastructure (c), and integrates them into a multi-core processor (d). A patching-aware compiler maintains a database of C-Core specifications and generates binaries that execute on a combination of C-Cores and the local CPU. The compiler (e) generates a patching configuration that allows the C-Cores to run future (and past) versions of the original applications.

While hardware release cycles are long, software release cycles are often much more rapid. Our design vision for C-Cores takes this into account in two key ways: First, we limit the non-recurring engineering costs for successive generations of C-Core enabled systems through automation. It is not feasible to rely on manual specification of every hot spot in every workload every time a new system is designed. Therefore, we have heavily automated this process. Second, we ensure that a C-Core enabled system can retain the utility of its C-Cores over the expected lifetime of the system. For this, we rely heavily on the patching mechanisms proposed in [VSG<sup>+</sup>10], and automatic generation of the requisite patches via our compiler infrastructure.

Figure 3.3 depicts the generation of a many-core processor equipped with C-Cores and the toolchain needed to target them. The process starts with the

processor designer characterizing the workload. This requires identifying applications that make up a significant fraction of the processor's target workload. The toolchain begins by extracting from these applications the most frequently used (or "hot") code regions (a). It then augments them with a small amount of reconfigurability (b) and synthesizes C-Core hardware using a 45 nm standard cell CAD flow (c). A single processor contains many tiles, each with a general purpose CPU and collection of different C-Cores (d).

In order to generate code for the processor, we extend a standard compiler infrastructure to support automatic code generation for C-Cores. In our case, we use a combination of LLVM [LA04], OpenIMPACT [Ope] and GCC. Any standard compiler infrastructure such as GCC, the Intel C++ compiler, or Microsoft Visual Studio would have been suitable. The compiler incorporates a description of the C-Core that the manufacturer has shipped silicon for. The compiler uses a matching algorithm to find similarities between the input code and the C-Core specifications (e). In cases where there are close matches, the compiler will generate both CPUonly object code and object code that makes use of the C-Core. The latter version of the code includes patching information that is downloaded into the C-Core via scan chains. This transfer occurs before the C-Core is invoked. The decision of whether to use the C-Core-enabled version of the code or the "software-only" version is made at run time, based on C-Core availability and other factors.

The next several sections describe how we turn our design vision into a concrete system. Section 3.3 describes the C-Core architecture. Sections 3.5, 3.6, and 3.4 detail our toolchain for automating the C-Core life cycle. We focus first on our system level architecture.

# **3.3** Conservation core architecture

This section describes the architecture of a C-Core-enabled system in more detail. We describe the organization of the C-Cores themselves and the interface between the C-Cores and the rest of the system.

#### 3.3.1 Conservation core organization

Each C-Core acts as a drop-in replacement for a region of code. An individual C-Core comprises a datapath and control state machine derived directly from the code it targets. Figure 3.1(c) shows the architecture of a prototypical C-Core. The principle components are the datapath, the control unit, the cache interface, and the scan chain interface to the CPU. The scan chain interface provides access to internal state. Specialized load and store units share ports to memory and use a simple token-based protocol to enforce correct memory ordering. For simplicity of correctness in our C-Core prototypes, this protocol restricts the number of concurrent memory accesses to one. Later, in Chapter 4, we will investigate performance optimizations for the memory ordering interface.

**Datapath and control** By design, the C-Core datapath and control very closely resemble the internal representation that our toolchain extracts from the C source code. The datapath contains the functional units (adders, shifters, etc.), the muxes to implement control decisions, and the registers to hold program values across clock cycles.

The control unit implements a state machine that mimics the control flow graph of the code. Every basic block in the code's original CFG has at least one corresponding state in the C-Core's control unit. Where there are memory or other variable latency operations within a basic block, the basic block is partitioned into multiple basic blocks. One control state is then created for every basic block in the new CFG. The control unit tracks branch outcomes (computed in the datapath) to determine which state to enter on each cycle. The control path sets the enable and select lines on the registers and muxes so that the correct basic block is active each cycle.

The close correspondence between the program's structure and the C-Core is important for two reasons: First, it makes it easier to enforce correct memory ordering in irregular programs. The ordering that the control path's state machine enforces corresponds to the order that the program counter provides in general purpose processors. We use that ordering to enforce memory dependencies. Second, close correspondence enhances robustness. Structural similarity improves the likelihood that small changes in the source code (which are the common case) will require correspondingly small reconfiguration facilities from the hardware. This maximizes the probability that the patching mechanisms from [VSG<sup>+</sup>10] will provide sufficient flexibility to adapt to the application changes.

To maintain this correspondence and to reduce the number of registers required in the datapath, the registers in the C-Core datapaths adhere to SSA form: Each static SSA variable has a corresponding register. This invariant minimizes the number of register updates: Exactly one register value changes per new value that the program generates.

Memory interface and ordering Memory operations require special attention to ensure that the C-Core enforces memory ordering constraints. Our prototype conservation cores enforce these constraints by allowing only one memory operation per basic block. The C-Core only activates one basic block at a time, guaranteeing that memory operations within the C-Core execute in the correct order. During C-Core execution, the CPU is inactive and all CPU accesses will have completed before C-Core execution begins or resumes. Thus, as both C-Cores and the CPU access the same cache, ordering between CPU and C-Core memory accesses is trivially maintained, although this does limit potential memory optimizations for the C-Core.

The load/store units connect to a coherent data cache. This ensures that all loads and stores are visible to the rest of the system regardless of which addresses the C-Core accesses.

Cache accesses can take multiple cycles. Moreover, the number of cycles is variable. To address this, the toolchain adds a self-loop to the basic block that contains each memory operation and exports a "valid" line to the control path. When the memory operation is complete, it asserts the "valid" signal and control exits the loop and proceeds with the following basic block. The "valid" signal is similar to the memory ordering token used in systems such as Tartan [MCC<sup>+</sup>06] and WaveScalar [SSM<sup>+</sup>07].

Most of the communication between C-Cores and the CPU occurs via the

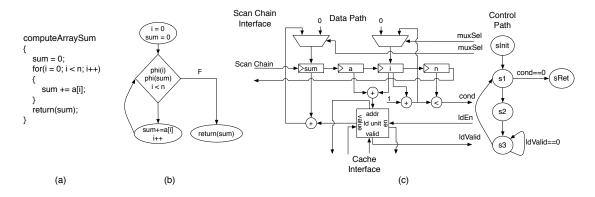

Figure 3.4: **Conservation core example** An example showing the translation from C code (a), to the compiler's internal representation (b), and finally to hardware (c). The hardware schematic and state machine correspond very closely to the data and control flow graphs of the C code.

shared L1 cache. A coherent, shared memory interface allows us to construct C-Cores for applications with unpredictable access patterns. Conventional accelerators cannot speed up these applications, because they cannot extract enough memory parallelism. Such applications can be an excellent fit for C-Cores, however, as performance is not the primary concern. Since the CPU and C-Cores do not simultaneously access the cache, the impact on the CPU cycle time is negligible.

**Multi-cycle instructions** Conservation cores handle other multi-cycle instructions (e.g., integer division and floating point operations) in the same way as memory operations. Each multi-cycle instruction resides in a basic block with a self-loop and generates a "valid" signal when it completes.

**Example** Figure 3.4 shows the translation from C source code (a) to hardware schematic and state machine (c). The hardware corresponds very closely to the CFG of the sample code (b). It has muxes for variables i and sum corresponding to the *phi* operators in the CFG. Also, the state machine of the C-Core is almost identical to the CFG, but with additional self-loops for multi-cycle operations. The datapath has a load unit to access the memory hierarchy to read the array a.

#### 3.3.2 The CPU/C-Core interface

Aside from the cache, the only connection between the CPU and the C-Cores is a set of scan chains. These scan chains are the mechanism that allows the CPU access to all of the C-Core's internal state. The CPU side of the interface is shared among all C-Cores on the CPU's tile. The CPU can communicate via scan chains with only one C-Core at a time, with switching controlled by the CPU. The CPU uses the scan chains to install patches that will be used across many invocations, and to pass initial arguments for individual invocations. The scan chains also allow the CPU to read and modify internal C-Core state to implement exceptions.

Conservation core scan chains are divided into two groups, fixed-function and data. There are a small number of short, fixed-function scan chains for control, argument passing, and patch installation. The bulk of the scan chains provide access to datapath registers. A C-Core may have up to 32 such data scan chains.

The scan chains for arguments are short (just 64 bits) to make invocation fast, but the patch installation scan chains can be much longer. In our biggest C-Core prototype, the patch chains reach up to 12,772 bits. However, patch installation is infrequent, so the cost of accessing the scan chain is minor: In general usage, patches will only be installed once per program invocation. A special "master control" scan chain contains a single bit and allows the CPU to start and stop the C-Core's execution as needed.

Datapath scan chains allow the CPU to manipulate arbitrary execution state during an exception. Datapath scan chains range in length from 32 to 448 bits in our largest C-Core.

To access the interface, the CPU provides three new instructions: Move-From-ScanChain (MFSC), Move-To-ScanChain (MTSC), and ScanChain-Rotate-Left (SCRL). MFSC moves the 32 bits at the head of a scan chain into a general purpose processor register, and MTSC does the reverse. SCRL rotates a scan chain left by n bits. SCRL executes asynchronously but MFSC and MTSC have blocking semantics: They will wait for previously issued SCRLs on a scan chain to finish before returning a value from that scan chain. As the C-Cores are drop-in replacements for existing code, programs need not block if the correct C-Core is not available (i.e., if it is in use by another program or currently configured with the incorrect patch). The original CPU (software) implementation is still available, and the program can use it instead.

# 3.4 Patching conservation cores

When a C-Core-equipped processor ships, it can run the latest versions of the targeted applications without modification. We refer to this version as the *original*. When a new version of an application becomes available, our toolchain must determine how to map the new version of the software onto the existing C-Core hardware. We refer to the new version of the software as the *target*. The goal of the patching process is to generate a *patch* for the original hardware that will let it run the target software version.

The longevity provided by patching is an important aspect of the C-Core life cycle. However, the details of the patching process are outside the scope of this dissertation. Below, we briefly describe how we support the patching approach from [VSG<sup>+</sup>10] in C-Cores.

#### 3.4.1 Integrating patching support

The bold box in Figure 3.5 shows how the patching system fits into the toolchain. We work directly on the program's dataflow and control graphs, a representation that can be generated from either source code or a compiled binary. Our implementation of the reconfiguration technique described in [VSG<sup>+</sup>10] provides C-Cores with three facilities to adjust their behavior after fabrication.

**Configurable constants** We generalize all hard-coded immediate values into configurable registers. This supports changes to the values of compile-time constants and the insertion, deletion, or rearrangement of structure fields.

Generalized single-cycle datapath operators To support the replacement of one operator with another, we generalize several operators. Any addition or subtraction is replaced by an adder-subtractor, any comparison operation by a generalized comparator, and any bit-wise operation by a bit-wise ALU. A small, four-bit configuration register is then added for each such operator, determining which operation is currently active.

**Control flow changes** In order to handle changes in the CFG's structure and changes to basic blocks that go beyond what the above mechanisms can handle, the C-Cores provide a flexible exception mechanism. The control path contains a bit for each state transition that determines whether the C-Core should treat it as an exception. This same mechanism is also used to handle system calls and other features not yet supported within our C-Core prototypes.

When the state machine makes an exceptional transition, the C-Core stops executing and transfers control to the general-purpose core. The exception handler begins by extracting current variable values from the C-Core via the scan-chainbased interface. It then executes the replacement code segment, transfers new values back into the C-Core, and resumes execution. The exception handler can restart C-Core execution at any point in the CFG, so exceptions can arbitrarily alter control flow and/or replace arbitrary portions of the CFG.

#### 3.4.2 Patch generation

The patching algorithm developed by Venkatesh, et al. [VSG<sup>+</sup>10] proceeds in four stages: basic block mapping, control flow mapping, register remapping, and patch generation. The details and implementation of the patching algorithm are outside the scope of this dissertation, but we will briefly describe its operation: The algorithm operates at basic block granularity. It identifies potential matches, based on internal structure, from basic blocks in the target versions to those in the original. Then, the CFG and a register renaming scheme are used to further refine whether two blocks are a match. Matching connected subgraphs of the CFG are then identified as *hardware regions*, portions of the target CFG that will execute in hardware. Remaining portions of the CFG are considered *software regions* and entry into them will be treated as an exception. Once the patching algorithm has identified all such regions, our toolchain can begin patch generation.

At this point we have all the information required to generate a patch that will let the target code run on the original hardware. The patch itself consists of three parts:

- the configuration bits for each of the configurable datapath elements along with values for each of the configurable constant registers

- exception bits for each of the control flow edges that pass from a hardware region into a software region

- code to implement each of the software regions

The software region code is subdivided into three sections. First, the *pro-logue* uses the scan chain interface to retrieve values from the C-Core's datapath into the processor core. Next, the *patch code* implements the software region. The region may have multiple exit points, each leading back to a different point in the datapath. At exit, the *epilogue* uses the scan chain interface again to insert the results back into the datapath and return control to the C-Core.

# 3.5 C-Core selection

In order to evaluate a prototype C-Core-enabled system, we must first construct a set of C-Core prototypes. Over the course of the following sections, we will show how we have developed our automated toolchain to support each phase of a C-Core's life cycle. We also discuss the measurement and validation infrastructure built into our toolchain that provides the data used throughout this dissertation. We begin with the selection phase of the C-Core life cycle.

To select regions of code appropriate for transforming into C-Cores, we must accurately estimate the area and energy-saving potential of software to hardware conversion. This includes identifying key and constraining overheads. The overhead of transferring control to and from the C-Core is an important factor in C-Core selection. This overhead places a lower bound on how much work a C-Core must do to achieve net benefits. It also limits how frequently we can use the exception mechanism during patching without nullifying the C-Core's energy gains.

To quantify this cost, we created a C-Core that returns immediately and executed it in a tight loop. The results show that transferring control to and from the C-Core takes, on average, 317 cycles or 211 ns. Of this, the stub function that invokes the C-Core accounts for 63%. Using the scan chains to pass arguments and return values to and from the C-Core accounts for the remaining 37%.

The exception cost likewise affects selection criteria for C-Cores using the exception mechanism to perform system calls or other features currently not directly supported on C-Cores. To quantify this cost, we synthesized a simple C-Core that executed an empty loop. We compared the run time of the C-Core with a patched version of the same C-Core. The patched version used the exception mechanism to transfer control to the CPU and directly back again. The transfer takes 260 cycles (173 ns) on average.

With invocation and exception overheads known, we can filter the list of high-coverage code regions and target the appropriate levels of the call-graph. We have implemented a completely automated tool for C-Core selection and isolation, but it has so far proved difficult to fine-tune. For the results throughout this dissertation, we instead rely on a hybrid method for C-Core selection. After automatic profiling, there is a manual review of the suggested code regions, filtering out any problematic selections. The filtered list is then fed back into the toolchain, which will automatically perform all processing required to turn those selected code regions into C-Cores.

# 3.6 Automatic Synthesis of C-Cores

Our C-Core synthesis toolchain automatically transforms portions of C programs into silicon. In the previous section, we discussed how hot regions are profiled and marked for extraction. Once we have wrapped these functions with stubs, we compile them into an intermediate three-address representation. We split these functions into datapath and control segments, and then uses a state-of-the-art EDA tool flow to generate a circuit fully realizable in silicon. The toolchain also generates a cycle-accurate system simulator for the new hardware. We use the simulator for performance measurements and to generate traces that drive Synopsys VCS and PrimeTime simulation of the placed-and-routed netlist. Below, we describe these components in more detail.

#### 3.6.1 Compilation Toolchain

Figure 3.5 summarizes the C-Core toolchain. The toolchain is based on the OpenIMPACT (1.0rc4) [Ope], CodeSurfer (2.1p1) [Cod], and LLVM (2.4) [LA04] compiler infrastructures. It accepts a large subset of the C language, including arbitrary pointer references, switch statements, and loops with complex conditions.

In the C-Core identification stage, functions or subregions of functions (e.g., key loops) are tagged for conversion into C-Cores based on profile information. The toolchain uses outlining to isolate the region and then uses exhaustive inlining to remove function calls. We pass global variables by reference as additional input arguments.

The C-to-Verilog stage generates the control and dataflow graphs for the function in SSA [CFR<sup>+</sup>89] form. This stage then adds basic blocks and control states for each memory operation and multi-cycle instruction. The final step of the C-to-Verilog stage generates synthesizeable Verilog for the C-Core. This requires converting  $\phi$  operators into muxes, inserting registers at the definition of each value, and adding self loops to the control flow graph for the multi-cycle operations. Then, it generates the control unit with a state machine that matches the control flow graph. This stage of the toolchain also generates a cycle-accurate module for our architectural simulator.

Figure 3.5: The C-Core C-to-hardware toolchain Our toolchain proceeds through hardware generation, patching, simulation, and power measurement over several stages. Program source enters our toolchain and passes through our C-Core selection stage, which identifies regions of code as C-Core candidates. Our C-to-Verilog compiler transforms these regions and produces a cycle-accurate simulator model for each region. Our simulator uses these models to produce traces, which we pass to VCS and PrimeTime to generate power results. The bold box contains the patch generation infrastructure based on our patching enabled compiler.

#### **3.6.2** Simulation infrastructure

Our cycle-accurate simulation infrastructure is based on *btl*, the Raw simulator [TLM<sup>+</sup>04]. We have modified btl to model a cache-coherent memory among multiple processors, to include a scan chain interface between the CPU and all of the local C-Cores, and to simulate the C-Cores themselves. The prototype C-Cores may operate at different clock frequencies from each other and from the core clock. These different cycle times are modeled in simulation by adjusting the duty cycle in clocking the C-Core.

In our prototype C-Core system model, the cache clock is synchronized to the C-Core when control is transferred to the C-Core. Minimum load-use latency for prototype C-Cores, as frequency is usually less than system frequency, is set at two C-Core cycles. In Chapter 4, we introduce a redesign of the C-Core pipeline such that all C-Cores operate synchronized with the system memory frequency, simplifying frequency modeling. Results in and after Chapter 4 presume a threecycle load-use latency, matching that of the CPU.

#### 3.6.3 Synthesis

For synthesis we target a TSMC 45 nm GS process using Synopsys Design Compiler (C-2009.06-SP2) and IC Compiler (C-2009.06-SP2). Our toolchain generates synthesizeable Verilog and automatically processes the design in the Synopsys CAD tool flow. The flow starts with netlist generation and continues through placement, clock tree synthesis, and routing before performing post-route optimizations. We specifically optimize for speed and power. We also make use of the Synopsys Module Compiler (C-2009.06-ICC-SP2), in order to generate technologyspecific custom functional units for basic arithmetic (addition, multiplication, etc.) and bit-shifting. These modules have been optimized for speed and power usage.

Figure 3.6 shows a placed and routed standard cell layout for an automatically generated prototype C-Core from the MCF 2006 application. Over 50% of the area is devoted to performing arithmetic operations in the datapath, 7% is dedicated to the control logic, and 40% is registers. This circuit meets timing at clock frequencies up to 1412 MHz.

Figure 3.6: MCF 2006 conservation core for primal\_bea\_mpp() function The C-Core synthesizes to  $0.077mm^2$ , operates at speeds up to 1412 MHz, and provides 53% coverage for the application. The light gray elements are datapath logic (adders, comparators, etc.), dark gray elements are registers, and the white elements constitute the control path.

#### **3.6.4** Power measurements

In order to measure C-Core power usage, our simulator periodically samples execution by storing traces of all inputs and outputs to the C-Core. Each sample starts with a "snapshot" recording the entire register state of the C-Core and continues for 10,000 cycles. The current sampling policy is to sample 10,000 out of every 50,000 cycles, and we discard sampling periods corresponding to the initialization phase of the application.

We feed each trace sample into the Synopsys VCS (C-2009.06) logic simulator. Along with the Verilog code our toolchain also automatically generates a Verilog testbench module for each C-Core. This testbench initiates the simulation of each sample by scanning in the register values from each trace snapshot. The VCS simulation generates a VCD activity file, which we pipe as input into Synopsys PrimeTime (C-2009.06-SP2). PrimeTime computes both the static and dynamic power for each sampling period. We model fine-grained clock gating for inactive C-Core states via post-processing.

# 3.7 Results