### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Configurable Energy-efficient Co-processors to Scale the Utilization Wall

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science

by

Ganesh Venkatesh

### Committee in charge:

Professor Steven Swanson, Co-Chair Professor Michael Taylor, Co-Chair Professor Pamela Cosman Professor Rajesh Gupta Professor Dean Tullsen

Copyright

Ganesh Venkatesh, 2011

All rights reserved.

| The dissertation of Ganesh Venkatesh is approved, and   |

|---------------------------------------------------------|

| it is acceptable in quality and form for publication on |

| microfilm and electronically:                           |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

| Co-Chair                                                |

|                                                         |

| Co-Chair                                                |

University of California, San Diego

2011

## DEDICATION

To my dear parents and my loving wife.

### EPIGRAPH

The lurking suspicion that something could be simplified is the world's richest source of rewarding challenges. —Edsger Dijkstra

## TABLE OF CONTENTS

| Signature Pa  | age .                         |                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .  |                               |                                                                                                                                                                                                                                                                                                                                                                             |

| Epigraph .    |                               |                                                                                                                                                                                                                                                                                                                                                                             |

| Table of Cor  | ntents                        |                                                                                                                                                                                                                                                                                                                                                                             |

| List of Figur | res .                         | ix                                                                                                                                                                                                                                                                                                                                                                          |

| List of Table | es                            |                                                                                                                                                                                                                                                                                                                                                                             |

| Acknowledge   | ement                         | s                                                                                                                                                                                                                                                                                                                                                                           |

| Vita and Pu   | blicat                        | ions                                                                                                                                                                                                                                                                                                                                                                        |

| Abstract of   | the Di                        | issertation                                                                                                                                                                                                                                                                                                                                                                 |

| Chapter 1     | Intro 1.1 1.2 1.3 1.4 1.5 1.6 | Utilization Wall Specialization for converting transistors into performance Patchable Conservation Cores: Energy efficient circuits with processor-like lifetimes Utilizing Conservation Cores to Design Mobile Application Processors Quasi-ASICs: Trading Area for Energy by Exploiting Similarity across Irregular Codes Organization  1 2 2 3 4 4 5 6 6 7 6 7 6 7 7 7 8 |

| Chapter 2     | Arse 2.1<br>2.2<br>2.3        | enal: Baseline Architecture and Tool Chain                                                                                                                                                                                                                                                                                                                                  |

|           | 4      | 2.3.3 Synthesis                                          | 18 |

|-----------|--------|----------------------------------------------------------|----|

|           | 4      | 2.3.4 Power measurements                                 | 18 |

| Chapter 3 | Patch  | able Conservation Cores: Energy-efficient circuits with  |    |

|           | proces | ssor-like lifetimes                                      | 20 |

|           | 3.1    | Case for Reconfigurability in Application                |    |

|           | ,      | Specific Circuits                                        | 21 |

|           | 3.2    | Reconfigurability support in Conservation                |    |

|           | (      | Cores                                                    | 24 |

|           | 3.3    |                                                          | 25 |

|           | ,      | 11 0                                                     | 27 |

|           | ,      | 11 0                                                     | 28 |

|           | ,      | 0 11 0                                                   | 29 |

|           | ,      | <u> </u>                                                 | 30 |

|           |        | ÷                                                        | 31 |

|           | 3.4    | <u> </u>                                                 | 31 |

|           | •      | 3.4.1 Generation of Patchable Conservation Core          |    |

|           |        |                                                          | 32 |

|           |        | 9 9                                                      | 32 |

|           | 3.5    |                                                          | 33 |

|           | ,      | 0                                                        | 33 |

|           |        | e v                                                      | 37 |

|           | 3.6    | v 1                                                      | 38 |

|           | •      | ů v                                                      | 38 |

|           |        |                                                          | 40 |

|           | 3.7    | 9                                                        | 43 |

|           | •      |                                                          | 47 |

|           |        |                                                          | 47 |

|           | 3.8    | Conclusion                                               | 50 |

| Chapter 4 | Utiliz | ing Conservation Cores to Design Mobile Application      |    |

| •         |        | <u> </u>                                                 | 53 |

|           |        |                                                          | 54 |

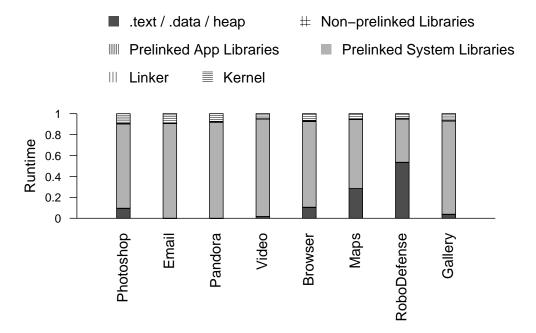

|           | 4      | 4.1.1 Android Platform Analysis                          | 54 |

|           | 4      | 1.1.2 Case for using c-cores to optimize mobile applica- |    |

|           |        | tion processors                                          | 56 |

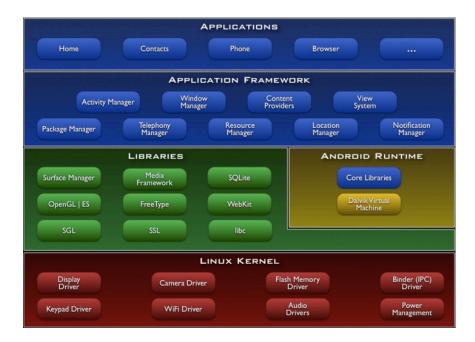

|           | 4.2    | Android Software Stack                                   | 56 |

|           | 4.3    | Designing Conservation Cores for Android                 | 58 |

|           |        |                                                          | 58 |

|           | 2      | · · · · · · · · · · · · · · · · · · ·                    | 59 |

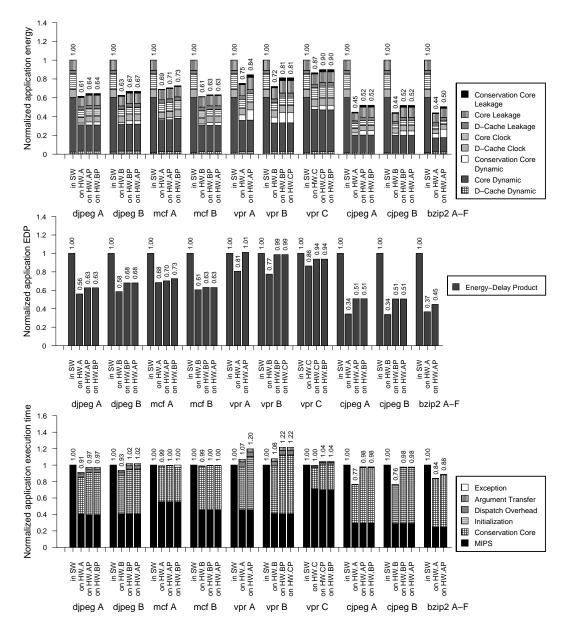

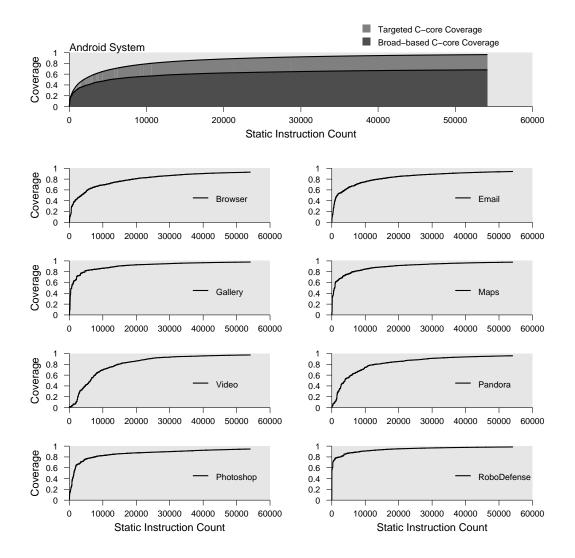

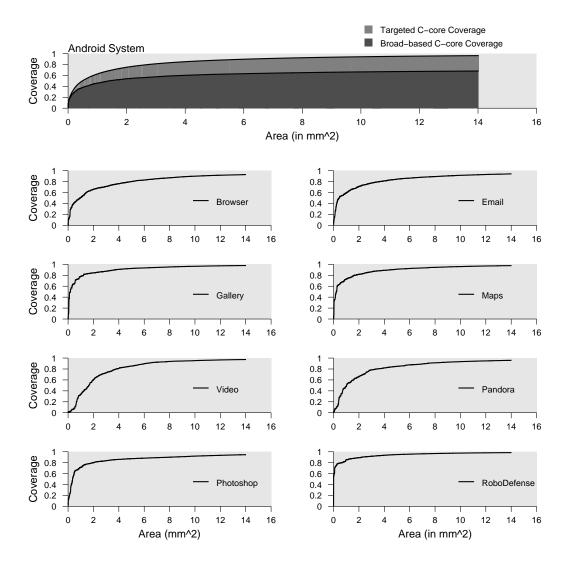

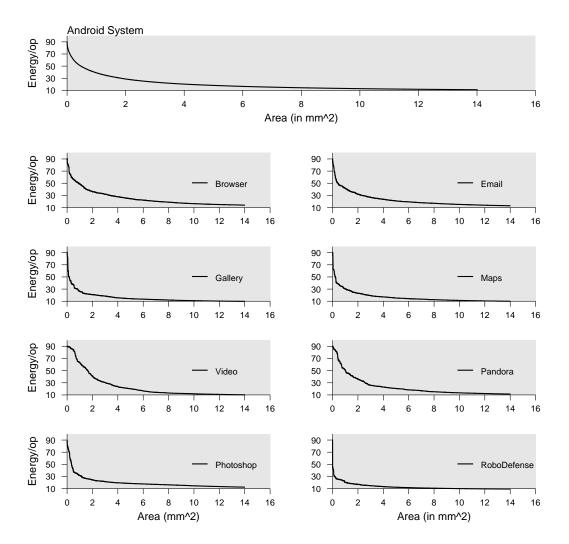

|           | 4.4    | Results                                                  | 67 |

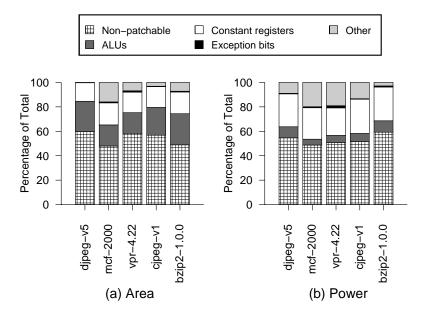

|           | 2      | 4.4.1 Area requirement                                   | 67 |

|           | 2      | 4.4.2 Energy-Area Tradeoff                               | 69 |

|              | 4.5 Conclusion                                              |

|--------------|-------------------------------------------------------------|

| Chapter 5    | Quasi-ASICs: Trading Area for Energy by Exploiting Similar- |

|              | ity across Irregular Codes                                  |

|              | 5.1 Motivation                                              |

|              | 5.2 Quasi-ASIC Design Flow                                  |

|              | 5.2.1 Dependence Graph Generation                           |

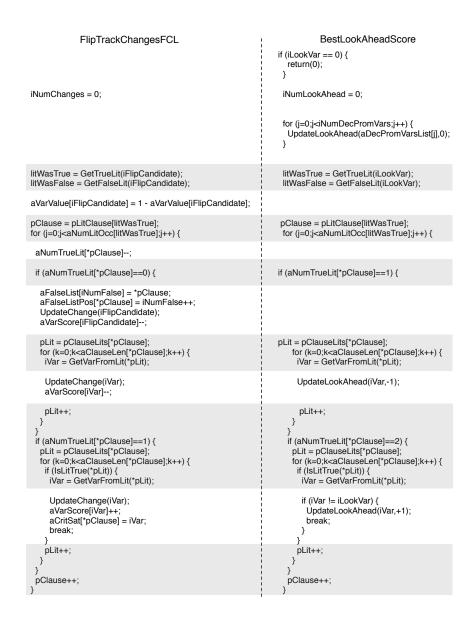

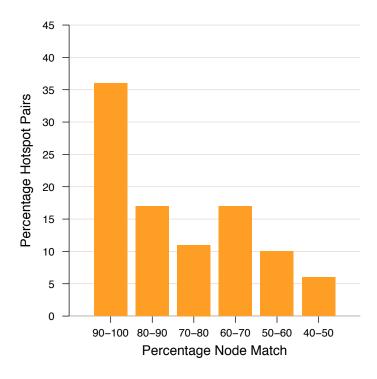

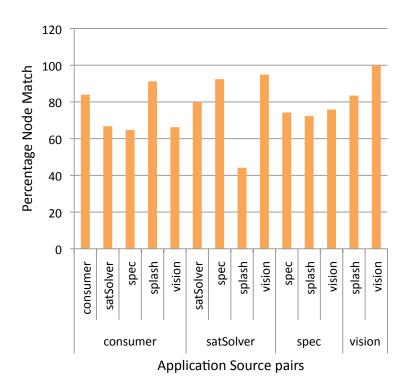

|              | 5.2.2 Mining for Similar Code Patterns                      |

|              | 5.2.3 Merging Program Dependence Graphs with simi-          |

|              | lar code structure                                          |

|              | 5.2.4 Qasic Generation                                      |

|              | 5.2.5 Modifying Application Code to utilize QASICs 9        |

|              | 5.3 Qasic-selection heuristic 9                             |

|              | 5.4 Methodology                                             |

|              | 5.4.1 Designing QASICs for the target application set . 9   |

|              | 5.4.2 QASIC Hardware Design 9                               |

|              | 5.5 Results                                                 |

|              | 5.5.1 Evaluating the QASIC-selection Heuristic 9            |

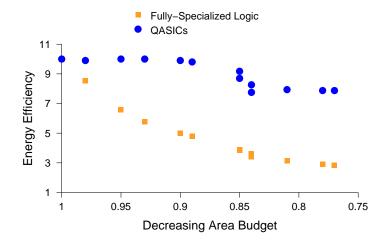

|              | 5.5.2 Evaluating Qasic's Area and Energy Efficiency . 9     |

|              | 5.6 Conclusion                                              |

| Chapter 6    | Related Work                                                |

|              | 6.1 Heterogeneous Architectures                             |

|              | 6.2 Automatically-designed Specialized Cores                |

| Chapter 7    | Summary                                                     |

| Bibliography | 11.                                                         |

### LIST OF FIGURES

| Figure 2.1: The high-level structure of an Arsenal system                            | 10       |

|--------------------------------------------------------------------------------------|----------|

| Figure 2.2: The high-level design flow of an Arsenal system                          | 11       |

| Figure 2.3: The high-level structure of the baseline architecture                    | 12       |

| Figure 2.4: Specialized Core Design Example                                          | 14       |

| Figure 2.5: The C-to-hardware toolchain                                              | 16       |

| Figure 3.1: Observed changes in the source code across application versions          | 23       |

| Figure 3.2: An example showing handling of changes in control flow across            | 00       |

| versions                                                                             | 26<br>27 |

| Figure 3.4: Patching Algorithm Toolchain                                             | 30       |

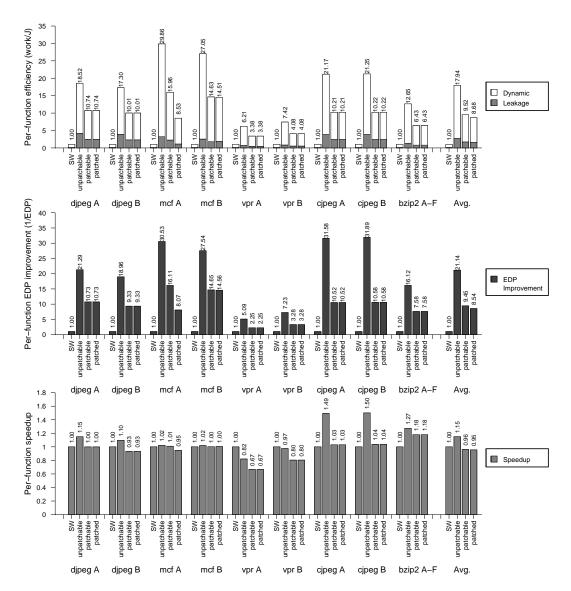

| Figure 3.5: Conservation Core versus MIPS Processor                                  | 35       |

|                                                                                      | 36       |

| e v                                                                                  | 37       |

|                                                                                      |          |

|                                                                                      | 39       |

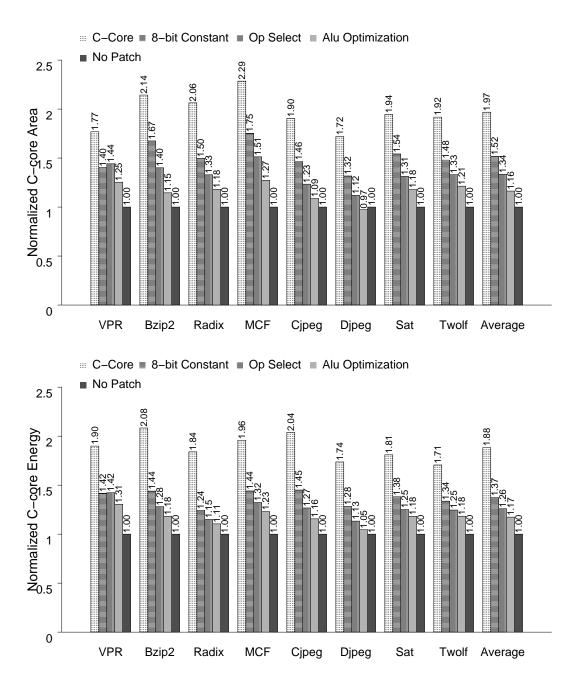

| Figure 3.9: Impact of patching optimizations on the area and energy re-              | 4.4      |

| quirements of patchable c-cores                                                      | 44       |

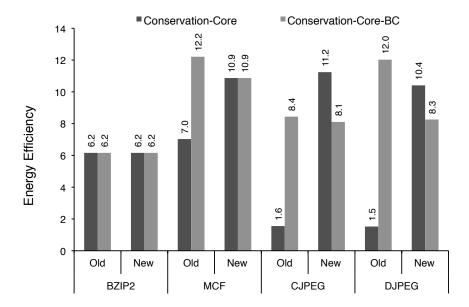

| Figure 3.10: Conservation Core design with improved backward compatibility guapa art | 45       |

| ity support                                                                          |          |

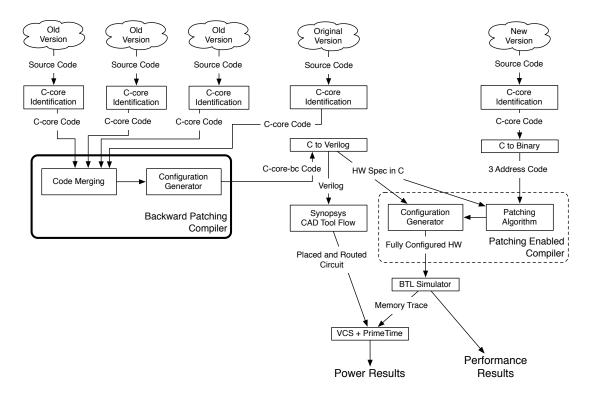

| Figure 3.11: The Backward Compatible Conservation Core Toolchain                     | 46       |

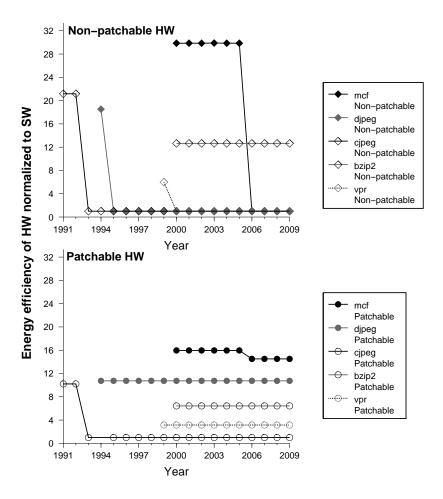

| Figure 3.12: Improvements in the backward compatibility of Conservation  Cores       | 48       |

|                                                                                      | 40       |

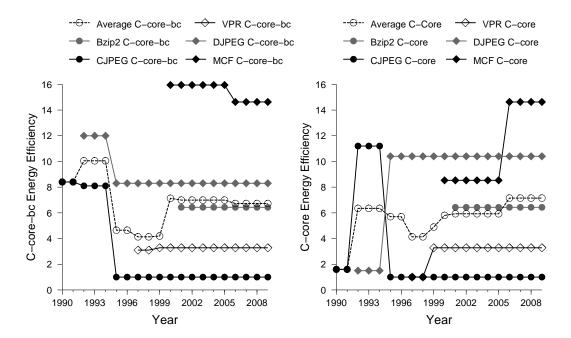

| Figure 3.13: Effectiveness of Backward Compatible Conservation Core over time        | 49       |

| time                                                                                 | 49       |

| Figure 4.1: Android Software Stack                                                   | 55       |

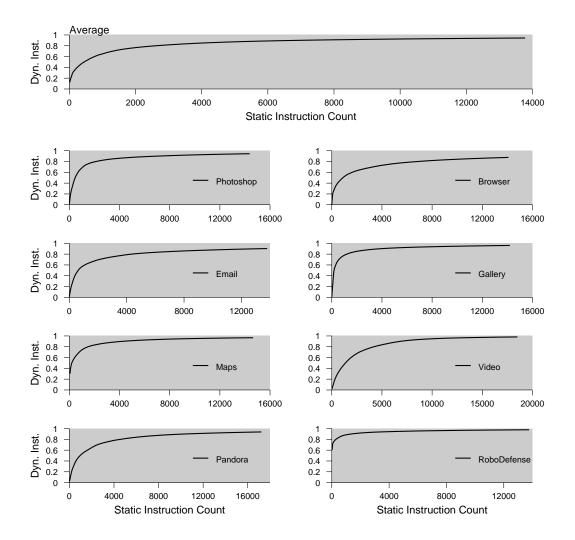

| Figure 4.2: Static Instruction Count vs Dynamic Instruction Count Coverage           | 60       |

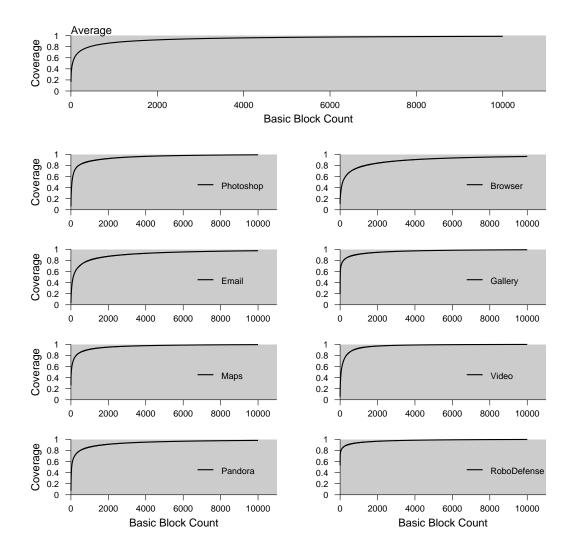

| Figure 4.3: Basic block count vs Application execution coverage                      | 61       |

|                                                                                      | 62       |

| Figure 4.5: Dynamic Execution Coverage vs Static Instructions Converted              |          |

| into Conservation cores                                                              | 66       |

| Figure 4.6: Android Execution Coverage vs Conservation core Area                     | 68       |

| Figure 4.7: Android Execution Coverage vs Conservation core Area                     | 70       |

| Figure 5.1: Qasic's ability to trade off between area and energy efficiency.         | 75       |

| Figure 5.2: Similar code patterns present across the hotspots of a Sat Solver        |          |

| tool                                                                                 | 77       |

| Figure 5.3: Similarity available across hotspots of diverse application set          | 70       |

| (Table 5.1)                                                                          | 79       |

| Domains                                                                              | 80       |

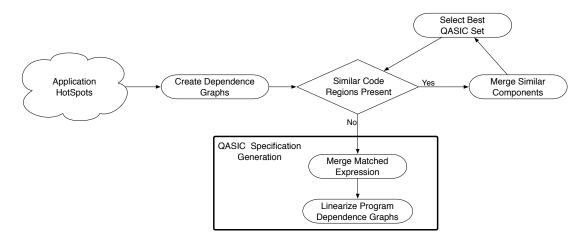

| Figure 5.5: | Qasic Design Flow                                               |

|-------------|-----------------------------------------------------------------|

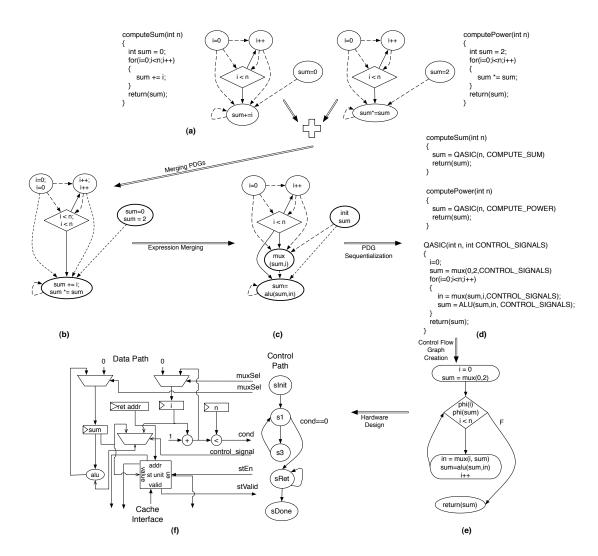

|             | Qasic Example                                                   |

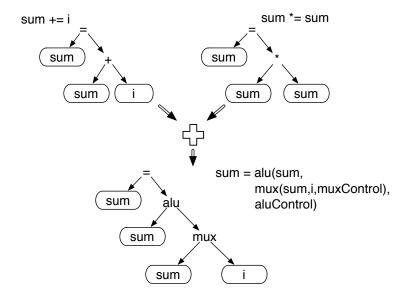

|             | Expression Merging                                              |

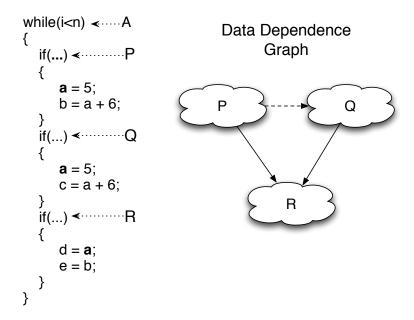

| Figure 5.8: | Inferred Dependence Example                                     |

| Figure 5.9: | Greedy Clustering Algorithm for Designing QASICS 92             |

| Figure 5.10 | : Qasic Toolchain                                               |

| Figure 5.11 | : Micro-Benchmark Set: Eight simple loops 95                    |

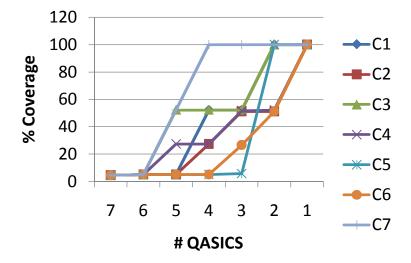

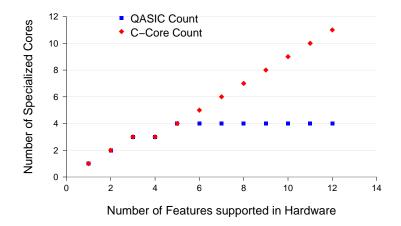

| Figure 5.12 | : Coverage vs Qasic count                                       |

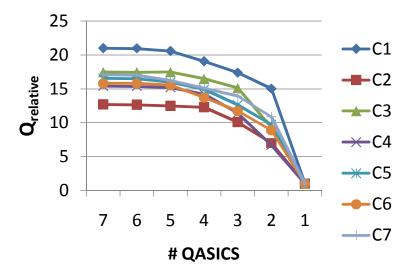

| Figure 5.13 | : Qasic quality vs. Qasic Count                                 |

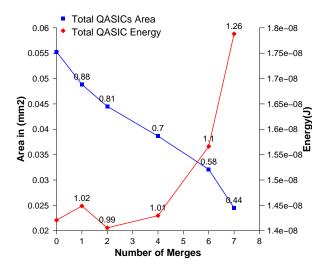

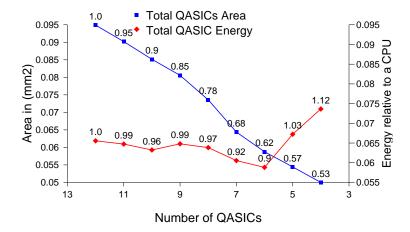

| Figure 5.14 | : Impact of generalization on QASIC Area and Energy Efficiency  |

|             | for the Micro-benchmarks                                        |

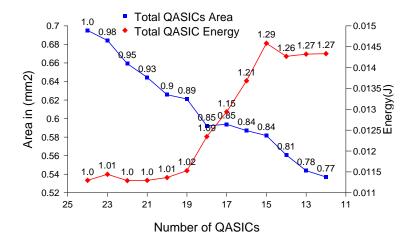

| Figure 5.15 | : Impact of generalization on the area and energy Efficiency of |

|             | Qasics targeting commonly used data structures 99               |

| Figure 5.16 | : Scalability of Qasic's approach                               |

| Figure 5.17 | : Impact of generalization on QASIC Area and Energy Efficiency  |

|             | for the Benchmark Set                                           |

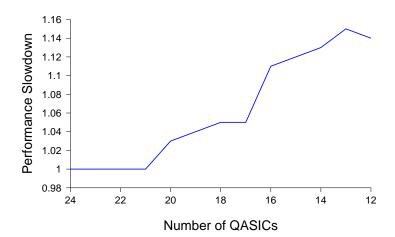

| Figure 5.18 | : Impact of generalization on QASIC Performance for our Bench-  |

|             | mark Set                                                        |

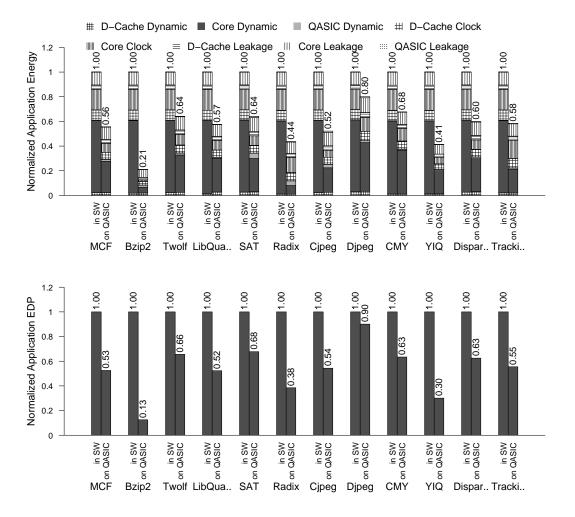

| Figure 5.19 | Energy efficiency of a QASIC-enabled system                     |

## LIST OF TABLES

| Table 1.1: | The Utilization Wall         |    |

|------------|------------------------------|----|

|            | Conservation core statistics |    |

|            | Conservation core details    |    |

| Table 3.3: | Area costs of patchability   | 11 |

| Table 5.1: | A Diverse Application Set    | 78 |

### ACKNOWLEDGEMENTS

This thesis would not have been possible without my advisors, Steven Swanson and Michael Taylor. My work would not have been this successful without their constant feedback and forward-looking approach to research. They taught me the value of patience, especially when working on an ambitious, work-intensive project.

I also owe this thesis to my former advisor, Bradley Calder. His guidance during my initial Ph.D. years played a critical role in helping me mature as a researcher as well as value the importance of hard work and persistence.

I would like to thank my committee members for their helpful comments and feedback. I must also thank Julie Conner for being the most awesome and patient graduate student advisor.

I would like to thank my UCSD friends (Dian, Anshuman, Joel, Ravi, ...) for the random chats in the hallway, long ping pong/foosball/tennis sessions, dinners, movies, escaping reality, etc. I also would like to thank my project mates for helping me through the highs and lows of my work and for all the long discussions during the initial stages of this work. Thanks to Nathan for his help with proofreading and tasty guacamole. Thanks to Jack for the many interesting conversations about "stuff" and for sharing his interesting culinary experiments. Thanks to Wei and Satish for all the late night hacking and tennis/foosball lessons. Thanks to Jeff for all the encouraging discussions and ph.d. advice. Thanks to Jeremy for teaching me how to eat watermelon. Thanks to Robert for all the long tennis discussions. Thanks to ...

I must heartily thank my parents and my wife. The greatest thing to come out of my stay at UCSD was meeting my wife, Sravanthi. She is a great source of strength in my life and has helped me through the stressful times of job hunt and thesis defense. Finally, I would like to thank my parents for all their love, for being there for me all these years, for teaching me the value of education as a kid, for inspiring me to pursue post graduate education, and many many other things. Thank you!

Chapters 2 and 3 contains material from "Conservation cores: reducing the energy of mature computations", by Ganesh Venkatesh, Jack Sampson, Nathan

Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson and Michael Bedford Taylor, which appears in ASPLOS '10: Proceedings of the fifteenth edition of ASPLOS on Architectural support for programming languages and operating systems. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

Chapter 3 contains material from "Efficient complex operators for irregular code", by Jack Sampson, Ganesh Venkatesh, Nathan Goulding, Saturnino Garcia, Steven Swanson and Michael Bedford Taylor, which appears in *HPCA '11:* Proceedings of the International Symposium on High-Performance Computer Architecture (HPCA). The dissertation author was the secondary investigator and author of this paper. The material in this chapter is copyright ©2011 by the Institute of Electrical and Electronics Engineers (IEEE). Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Chapter 4 contains material from "The GreenDroid mobile application processor: An architecture for silicons dark future", by Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Aurricchio, Po-Chao Huang, Manish Arora, Siddharth Nath, Vikram Bhatt, Jonathan Babb, Steven Swanson and Michael Bedford Taylor, which appears in *IEEE Micro*, March 2011. The disser-

tation author was a significant contributor and author of this paper. The material in this chapter is copyright ©2011 by the Institute of Electrical and Electronics Engineers (IEEE). Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

#### VITA AND PUBLICATIONS

B. Tech. in Computer Science

Indian Institute of Technology, Madras

2004-2011 Research assistant

University of California, San Diego

2005 Internship

Intel Labs

Santa Clara, California

2006 Internship

**HP** Labs

Palo Alto, California

2006 M. S. in Computer Science

University of California, San Diego

2011 Ph. D. in Computer Science

University of California, San Diego

#### **PUBLICATIONS**

Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson, Michael Bedford Taylor, "Conservation Cores: Reducing the Energy of Mature Computations", *Proceedings of the Fifteenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, March 2010.

Jack Sampson, Ganesh Venkatesh, Nathan Goulding, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor, "Efficient complex operators for irregular code", International Symposium on High-Performance Computer Architecture (HPCA), February 2011.

Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Aurricchio, Jonathan Babb, Michael Bedford Taylor, and Steven Swanson, "Green-Droid: A mobile application processor for a future of dark silicon", *Symposium for High Performance Chips (HotChips)*, August 2010.

Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Aurricchio, Po-Chao Huang, Manish Arora, Siddharth Nath, Vikram Bhatt, Jonathan Babb, Steven Swanson, and Michael Bedford Taylor, "The GreenDroid mobile application processor: An architecture for silicons dark future", *IEEE Micro*, March 2011.

Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Steven Swanson, and Michael Bedford Taylor, "Quasi-Asics: Trading area for energy by exploiting similarity in synthesized cores for irregular code", *UCSD Technical Report CS2011-0964*, March 2011.

#### ABSTRACT OF THE DISSERTATION

### Configurable Energy-efficient Co-processors to Scale the Utilization Wall

by

#### Ganesh Venkatesh

Doctor of Philosophy in Computer Science

University of California, San Diego, 2011

Professor Steven Swanson, Co-Chair Professor Michael Taylor, Co-Chair

Transistor density continues to increase exponentially, but the power dissipation per transistor improves only slightly with each generation of Moore's law. Given constant chip-level power budgets, this exponentially decreases the fraction of the transistors that can be active simultaneously with each technology generation. Hence, while the area budget continues to increase exponentially, the power budget has become a first-order design constraint in current processors. In this regime, utilizing transistors to design specialized cores that optimize energy-percomputation becomes an effective approach to improve the system performance.

To pursue this goal, this thesis focuses on specialized processors that reduce energy and energy-delay product for general purpose computing. The focus on energy makes these specialized cores an excellent match for many of the commonly used programs that would be poor candidates for SIMD-style hardware acceleration (e.g. compression, scheduling). However, there are many challenges, such as lack of flexibility and limited computational power, that limit how effective these specialized cores are at targeting general purpose computing. Without addressing these concerns, these specialized cores would be limited in the scope of applications that they can effectively target.

This thesis addresses these various challenges involved in making specialization a viable approach to optimize general-purpose computing. To this end, this thesis proposes Patchable Conservation Cores which are flexible, energy-efficient co-processors that contain the ability to be patched, enabling them to remain useful across versions of their target application. To demonstrate the effectiveness of these conservation cores in targeting a system workload, this thesis utilizes them to design a mobile application processor targeting the Android software stack. The results show that these specialized cores can cover a significant fraction of the system execution while staying within a modest area budget.

To further increase the fraction of the system execution that these specialized cores cover, this thesis proposes QASICs, specialized co-processors capable of executing multiple general-purpose computations. QASIC design flow exploits the similar code patterns present within and across applications to reduce redundancy across specialized cores as well as improve their computational power.

# Chapter 1

# Introduction

Transistor density continues to scale but per-transistor switching power is not scaling down anymore. As a result, given the fixed chip-level power budgets, the fraction of transistors that can be active at full frequency is decreasing exponentially with each generation of Moore's Law. This phenomenon is termed as the  $Utilization\ Wall\ [VSG^+10]$ . The utilization wall results in a dramatic increase in the amount of  $dark\ silicon\ -$  silicon that is underclocked or underused because of power concerns.

The utilization wall phenomenon is making it harder for designers to convert transistors into performance. Traditionally, increases in transistor counts were used to increase the application performance by designing faster and more optimized superscalar pipelines. However, concerns about the microarchitectural scalability of these superscalar pipeline designs motivated transition towards multi-core processors. Multi-core designs continued the system performance scaling by allowing multiple computations to run in parallel. However, the utilization wall phenomenon limits the effectiveness of these multi-core designs by constraining the fraction of the chip, and hence the number of computations, that can be simultaneously active.

Since utilizing the entire die simultaneously at full frequency is not possible any more, many of the recent proposals have focussed on specialization to address the problem of scaling system performance with transistor density. Specialized circuits are generally faster, and almost always more energy-efficient than their general-purpose counterparts. To date, however, few of the recent efforts focus on designing specialized circuits for the general-class of irregular integer programs. Also, most of the previous application-specific proposals design very narrowly defined co-processors that can only be used by their target application, and even for their target application, they cannot support changes across application versions. This thesis proposes mechanisms to provide reconfigurability and generality in application-specific circuits, that significantly enhances their longevity and enables them to support multiple applications with similar data/control flow.

### 1.1 Utilization Wall

This section examines the utilization wall in greater detail and demonstrates how the utilization wall is a consequence of CMOS scaling theory combined with modern technology constraints.

Scaling Theory Table 1.1 shows how the utilization wall emerges from the breakdown of classical CMOS scaling as set down by Dennard [DGR<sup>+</sup>74] in his 1974 paper. The equations in the "Classical Scaling" column governed scaling up until 130 nm, while the "Leakage Limited" equations govern scaling at 90 nm and below. CMOS scaling theory holds that transistor capacitances (and thus switching energy) decrease roughly by a factor of S (where S is the scaling factor, e.g.,  $1.4\times$ ) with each process shrink. At the same time, transistor switching frequency improves by S and the number of transistors on the die increases by  $S^2$ .

In the Classical Scaling Regime, it has been possible to scale supply voltage by 1/S, leading to constant power consumption for a fixed-size chip running at full frequency, and consequently, no utilization wall. Scaling the supply voltage requires that we also scale the threshold voltage proportionally. However, this is not an issue because leakage, although increasing exponentially, is not significant in this regime.

In the Leakage Limited Regime, it is no longer possible to scale the threshold voltage because leakage rises to unacceptable levels. Without the corresponding supply voltage scaling, reduced transistor capacitance is the only remaining

Table 1.1: The utilization wall The utilization wall is a consequence of CMOS scaling theory and current-day technology constraints, assuming fixed power and chip area. The Classical Scaling column assumes that  $V_t$  can be lowered arbitrarily. In the Leakage Limited case, constraints on  $V_t$ , necessary to prevent unmanageable leakage currents, hinder scaling, and create the utilization wall.

| Param.     | Description                       | Relation                         | Classical<br>Scaling | Leakage<br>Limited |

|------------|-----------------------------------|----------------------------------|----------------------|--------------------|

| В          | power budget                      |                                  | 1                    | 1                  |

| A          | chip size                         |                                  | 1                    | 1                  |

| $V_t$      | threshold voltage                 |                                  | 1/S                  | 1                  |

| $V_{dd}$   | supply voltage                    | $\sim V_t \times 3$              | 1/S                  | 1                  |

| $t_{ox}$   | oxide thickness                   |                                  | 1/S                  | 1/S                |

| W, L       | transistor dimensions             |                                  | 1/S                  | 1/S                |

| $I_{sat}$  | saturation current                | $WV_{dd}/t_{ox}$                 | 1/S                  | 1                  |

| p          | device power<br>at full frequency | $I_{sat}V_{dd}$                  | $1/S^2$              | 1                  |

| $C_{gate}$ | capacitance                       | $WL/t_{ox}$                      | 1/S                  | 1/S                |

| F          | device frequency                  | $\frac{I_{sat}}{C_{gate}V_{dd}}$ | S                    | S                  |

| D          | devices per chip                  | A/(WL)                           | $S^2$                | $S^2$              |

| P          | full die, full                    | $D \times p$                     | 1                    | $S^2$              |

|            | frequency power                   |                                  | 1                    |                    |

| U          | utilization at                    | B/P                              | 1                    | $1/\mathrm{S}^2$   |

|            | fixed power                       |                                  | _                    | 1,5                |

counterbalance to increased transistor frequencies and increasing transistor counts. Consequently, the net change in full chip, full frequency power is rising as  $S^2$ . This trend, combined with fixed power budgets, indicates that the fraction of a chip that can be run at full speed, or the utilization, is falling as  $1/S^2$ . Thus, the utilization wall is getting exponentially worse, increasing the fraction of dark silicon roughly by a factor of two, with each process generation.

# 1.2 Specialization for converting transistors into performance

One promising option to effectively utilize the dark silicon is to design a set of specialized processing elements tailored for specific applications. The specialized processors are more efficient than general-purpose processors (by several orders of magnitude for highly-specialized ASICs), and off-loading portions of a program to a specialized processor can realize large gains in energy-efficiency and performance. In this manner, the increases in transistor counts can be used to scale system performance by providing increased specialization as well as increasing the percentage of the system execution that runs on specialized processors.

Since the fraction of dark silicon continues to increase exponentially with each technology generation, the area available for specialized processors will increase accordingly. To utilize this increasing transistor budget effectively, designers must provide an ever increasing amount of specialization with each process generation. To accomplish this, these specialized processors must be designed automatically, enabling the designers to target a greater percentage of the workload execution with increases in transistor counts.

Existing approaches for automatically designing specialized processors primarily seek to build accelerators for regular, streaming loops with predictable control-flow and memory access patterns [YGBT09, FKDM09, CHM08]. While these applications are important, they are significantly different from the general class of irregular integer applications that are important on the desktop. The irregular integer programs are poor candidates for acceleration via specialized hardware

because they tend to have much larger hotspots with irregular, hard-to-predict control flow and memory-access patterns. This is the class of applications that this thesis focuses on and proposes specialized cores for them. These specialized cores provide significant energy-efficiency compared to general-purpose processors and greater configurability than fully-specialized logic. These energy-efficient specialized processors improve the system performance with increasing transistor counts by optimizing energy-per-computation, and hence allowing more computations to run in parallel.

Next, we introduce the three main parts of this thesis – 1) Patchable Conservation Cores (c-cores) [VSG<sup>+</sup>10, SVG<sup>+</sup>11], energy-efficient application-specific circuits with targeted reconfigurability to support changes in source code across application versions, 2) Application of the Conservation Cores in designing Mobile Application Processors [GSV<sup>+</sup>10, GSV<sup>+</sup>11], and 3) QASICs [VSG<sup>+</sup>11], energy-efficient circuits to make the area-energy tradeoff scalable by exploiting similar code patterns across irregular codes.

# 1.3 Patchable Conservation Cores: Energy efficient circuits with processor-like lifetimes

To effectively target the hotspots of general-purpose applications, specialized circuits must be able to support complex C constructs and must have lifetimes comparable to those of general-purpose processors. In order to have long lifetimes, the specialized circuits must remain useful across application versions by supporting code changes such as changes in the expression constants, memory layout and control flow.

Traditionally, application-specific circuits are very narrowly defined and cannot support any change in the target source code. This inability to support code changes make ASICs poor candidates for targeting any application that may have new version releases. This brittleness of ASICs is one of the main obstacles in their adoption by system designers to target even the mature and very commonly used applications.

The key contribution of the Patchable Conservation Core work is to provide application-specific circuits with reconfigurability mechanisms that would enable them to support the source code changes that are commonly seen across application versions. Conservation Cores support changes in the control-flow, expression constants, arithmetic operators, and memory layout of data structures. The conservation core tool chain automatically generates "configuration patches" for the new application versions and the conservation core is initialized at the runtime with the configuration patch corresponding to the application version that is going to execute on them. This ensures that these conservation cores do not bind the system users to any particular application version.

# 1.4 Utilizing Conservation Cores to Design Mobile Application Processors

Specialization has played a major role in the rapid advances in mobile device capabilities in the recent past. Specialized hardware enables the mobile devices to provide rich user experience, enabling the user to stay connected, stream multimedia, play games, and navigate using GPS-powered maps. As a result of this improved functionality, the market for smartphones and other portable devices is growing rapidly and these mobile devices are expected to outsell desktop PCs in the coming years [IDC]. To ensure that this growth continues, mobile devices will need to provide greater functionality with each generation without compromising on the battery life.

Traditionally, mobile platforms exploit manually-designed specialized hardware to address power concerns and achieve better performance by integrating specialized cores on an SoC. However, emergence of the new generation of mobile devices such as those based on Apple iOS and Google Android run an increasingly diverse collection of applications, straining the traditional model of manually designed specialized hardware. In order to support this increasing functionality, a new generation of mobile devices must rely on general-purpose application processors. However, the utilization wall threatens to limit the performance scaling of application processors, impeding the evolution of what is becoming the dominant computing platform for much of the world.

This thesis explores the use of conservation cores to design these energy-efficient mobile application processors. In particular, this project analyzes the potential for using conservation cores to design application processors for Android-based mobile devices. This work demonstrates that our conservation core-based approach is a good match for the Android platform. The results show that c-cores were able to cover a significant fraction of system execution and provide significant energy savings without exceeding the modest area budgets.

# 1.5 Quasi-ASICs: Trading Area for Energy by Exploiting Similarity across Irregular Codes

Specialized circuits enable system designers to trade area for energy efficiency. However, for many applications in a system's workload, it is not scalable to trade silicon for a specialized co-processor that can only execute a hotspot of an application. Hence, system designers need to decide on the amount of specialization required based on the available area budget and the relative importance of applications in the system's workload.

Existing approaches for designing ASICs tend to design specialized processors that only target a specific piece of code. Hence, to fit within a given area budget, system designers would need to remove specialization corresponding to some of the computations used by the system workload. However, this reduction in the fraction of system execution covered by specialized processors can significantly decrease the system's energy efficiency since the application specific circuits tend to be more energy-efficient than general-purpose processors by a few orders of magnitude.

This thesis proposes a new class of specialized circuits, *Quasi-ASICs* (QASICs), that enable the system designers to vary the amount of hardware generality based on the available area budget. The key contribution of the QASIC work is the insight that similar code patterns exist within and across applications and

these similar code segments can be exploited to reduce the area requirements without removing functionality. The QASIC tool chain mines for similar computations across the system workload and builds a configurable circuit that can execute all of them. As a result, our approach makes the area-energy tradeoff more scalable by designing specialized processors that support multiple general-purpose applications while providing energy efficiency comparable to fully specialized logic.

# 1.6 Organization

Chapter 2 presents the baseline architecture that this work builds on as well as the methodology to evaluate the performance and energy efficiency of the system. Chapter 3 describes Patchable Conservation Cores and shows how their flexibility enables them to support newer versions of their target application. This chapter also discusses optimizations to reduce the area and energy overheads of adding flexibility in specialized circuits as well as improve the backward compatibility of conservation cores. Chapter 4 demonstrates that these patchable conservation cores can significantly improve the energy efficiency of mobile application processors. Chapter 5 describes QASICs and discusses how they can trade area for energy efficiency in a scalable manner. Chapter 6 presents the previous work on designing heterogeneous architectures as well as work on high-level synthesis. Chapter 7 concludes.

# Acknowledgments

Portions of this research were funded by the US National Science Foundation under NSF CAREER Awards 06483880 and 0846152, and under NSF CCF Award 0811794.

# Chapter 2

# Arsenal: Baseline Architecture and Tool Chain

This thesis builds on the Arsenal processor, a massively heterogeneous multiprocessor [Ars]. This chapter provides a high level overview of the Arsenal system, the baseline heterogeneous tiled architecture used in this thesis for performance and energy analysis as well as the toolchain for automating the design of specialized hardware from C source code.

# 2.1 Arsenal: Massively Heterogeneous Multiprocessors

This section provides an overview of the Arsenal processor including their design goals, high-level hardware organization, and execution model.

The main goal of the Arsenal processor design is to ensure that the system performance scales with the increases in transistor counts in spite of the utilization wall. Arsenal designs are comprised of 10s to 100s to even 1000s of heterogeneous specialized processing elements (SPEs), ranging from specialized processors dedicated to particular loop nests, to 8-way issue DSPs, graphics accelerators, and to out-of-order superscalars. Although the utilization wall dictates that Arsenal systems may use only a small fraction of the die at once, it uses that fraction very

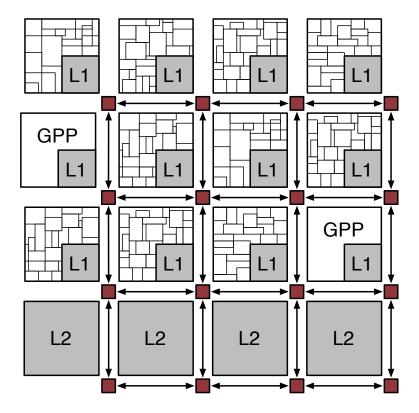

Figure 2.1: The high-level structure of an Arsenal system An Arsenal system is made up of multiple SPE "complexes" (i.e. tiles).

efficiently. The Arsenal system achieves this efficiency by dynamically varying which fraction of the chip is active based on the applications that are executing on them.

# 2.1.1 Hardware Organization

Figure 2.1 depicts the high level design of an Arsenal processor comprised of twelve *SPE complexes* and four banks of shared L2 cache connected by a grid-based on chip interconnect. Together the complexes, cache banks, and network resemble recently proposed tiled processors such as Wavescalar [SMSO03], RAW [TLM+04], or TRIPS [SNL+03]. Instead of uniform tiles, however, the complexes (i.e., the "tiles") in an Arsenal processor contain many SPEs. The mix of SPEs in each complex is different. Arsenal systems organize SPEs into complexes (or tiles) based on related functions to allow pipeline-sequential style communication. SPEs

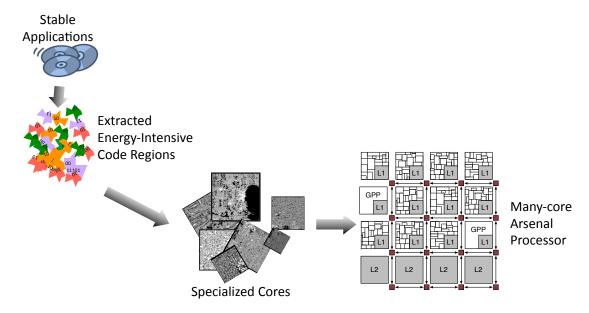

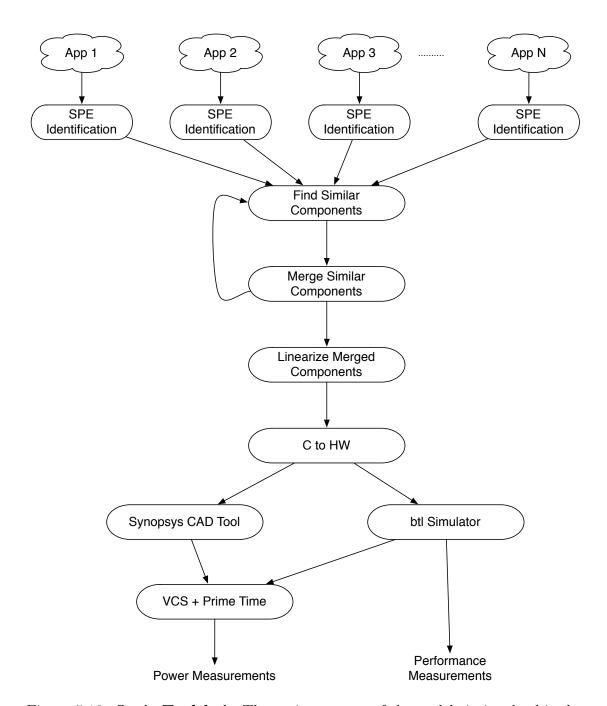

Figure 2.2: **High-level Design Flow of an Arsenal system** Arsenal system's design is customized for the applications that commonly run on them.

likely to be used in sequence are placed in the same complex, so that they can efficiently communicate through the local L1 cache.

## 2.1.2 Arsenal Design Flow

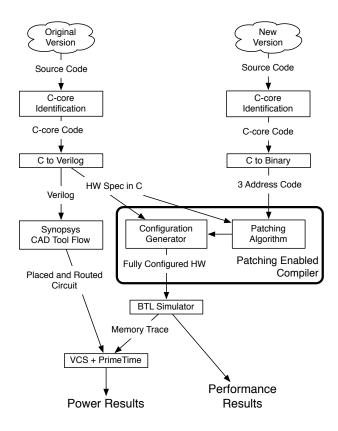

Figure 2.2 depicts the generation of a many-core Arsenal processor. The process begins with the processor designer characterizing the workload by identifying codes that make up a significant fraction of the processors target workload. The toolchain extracts the most frequently used (or hot) code regions and uses a high-level synthesis tool to design specialized cores corresponding to these hot regions. Finally, these specialized cores are integrated with a general-purpose processor to design a heterogeneous many-core system.

### 2.1.3 Execution Model

A program executing on an Arsenal processor migrates between SPEs as its behavior changes. The Arsenal toolchain and run-time environment combine to create the mapping between different sections of the program and the available

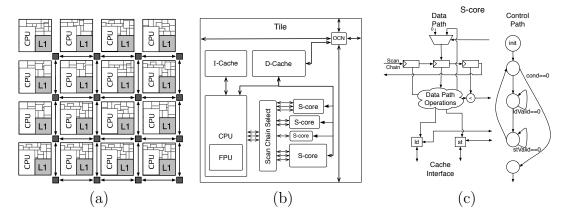

Figure 2.3: The high-level structure of the baseline architecture The baseline architecture (a) is made up of multiple individual tiles (b), each of which contains multiple application-specific circuits (S-cores) (c). These specialized circuits communicate with the rest of the system through a coherent memory system and a simple scan-chain-based interface. Not drawn to scale.

SPEs. Programmers and compilers can use a range of tools (e.g. library interfaces, code similarity measurement technology, and performance prediction models) to identify which code segments will run most efficiently on different SPEs. The run-time schedules code onto the available SPEs taking into account the physical location of the SPEs and other applications competing for the same SPEs. The mapping of programs to SPEs can also change at runtime to account for observed changes in program behavior.

# 2.2 System Overview

The particular instantiation of the Arsenal processor that this thesis studies as the baseline architecture is shown in Figure 2.3. It consists of an array of heterogeneous tiles. Each tile contains a general-purpose processor, I-Cache, D-Cache, set of specialized circuits, and interconnect logic.

A typical system includes 100s of specialized processors designed for key functions of the target workload set. On each tile, the specialized circuits are connected to the general-purpose processor via scan chains. The scan chain interface is slow but scales well enabling us to connect 10s of specialized circuits to

the general-purpose processor. The specialized circuits share the D-Cache with the general-purpose processor, ensuring coherent memory between the two by construction.

This architecture achieves much of its energy efficiency compared to a conventional tiled architecture system by offloading computations onto these specialized circuits. These circuits are automatically designed using a C-to-hardware compiler (Section 2.3) and achieves significant energy efficiency (up to  $40\times$ ) compared to a general-purpose processor.

### 2.2.1 Specialized Processor Hardware Design

This section describes in detail the architecture of the specialized circuits including their datapath, control unit, cache interface, and scan chain interface to the CPU.

**Datapath and Control Unit** By design, the datapath and control unit of the specialized circuits very closely resembles the data and control flow of the target source code in Single static assignment form [CFR<sup>+</sup>89]. The datapath contains functional units (adders, shifters, etc.) for the arithmetic operations, muxes to implement control decisions and phi [CFR<sup>+</sup>89] nodes, and registers to hold program values across clock cycles.

The control unit implements a state machine that mimics the control flow of the code. It tracks branch outcomes to determine which state to enter on each cycle. The control unit sets the enable and select lines on the registers and muxes so that the correct basic block is active each cycle.

The close correspondence between the program's structure and the corresponding specialized circuit enables them to support almost arbitrary source code including struct, union, pointers, and most control flow constructs. This design model fits well with the higher level goals of this thesis to provide energy-efficient execution for irregular, hard to parallelize integer applications.

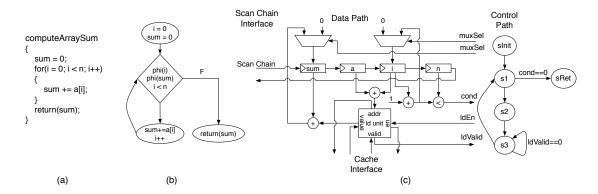

Figure 2.4: **Specialized Core Design Example** An example showing the translation from C code (a), to the compiler's internal representation (b), and finally to hardware (c). The hardware schematic and state machine correspond very closely to the data and control flow graphs of the C code.

Memory interface and ordering The specialized circuits execute the memory operations sequentially in the program order to ensure correctness. The specialized circuits contain a load/store unit for each memory operation in the target source code and these units connect to the processor's L1 data cache, guaranteeing a coherent memory system between the specialized circuit and CPU by construction. For executing a memory operation, the load/store unit sends a "request" signal along with the memory address/value to the L1 data cache and stalls the execution of the specialized processor until it receives the "valid" signal from the cache signaling the completion of the memory operation.

**Example** Figure 2.4(a)-(c) shows a sample source code, its control flow graph, and the corresponding hardware design for it. The hardware corresponds very closely to the CFG of the sample code. The datapath has muxes corresponding to the phi operators in the CFG. Also, the control unit is almost identical to the CFG, with additional self-loops for memory operations (and other multi-cycle operations). The datapath has a load unit to access the memory hierarchy to read the array a.

### 2.2.2 The CPU/Specialized-processor Interface

The specialized circuits are connected to the CPU via a set of scan chains. They receive the initial arguments as well as the "ready" signal from the CPU using these scan chains. The initial arguments are the live-in values for the computation being off-loaded to the specialized circuit and the ready signal signals the beginning of the execution. When the specialized circuits complete the off-loaded computation, they send a "done" signal to the CPU.

### 2.2.3 The Runtime System

When compiling an application containing functions that can be off-loaded to a specialized processor, the compiler will insert stubs that enable the application to choose between using the specialized processor or the CPU at runtime.

At runtime, when an application wants to run a function that has the corresponding specialized circuit available, it queries the runtime to get access to the specialized processor. If the specialized processor is available, the application uses the scan chain interface to pass the initial arguments, start it running, and then waits for execution to complete. When the done signal is raised by the specialized processor, control passes back to the stub code which extracts the return value and passes it back to the application.

If the specialized processor is not available, then the application uses the CPU version of the function code to continue execution on the general-purpose processor.

# 2.3 Methodology

This section presents the details of the toolchain for automatically generating the hardware for specialized cores from the application code as well as the methodology for the performance and power measurements of the baseline system.

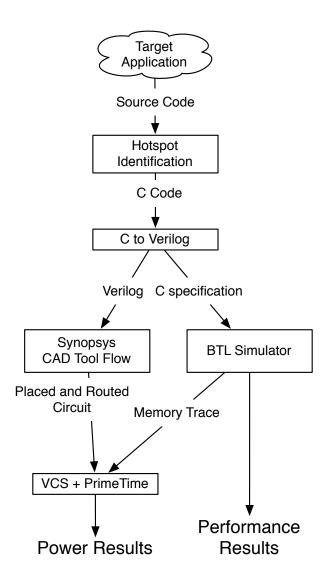

Figure 2.5: **The C-to-hardware toolchain** The various stages of our toolchain involved in hardware generation, simulation, and power measurement are shown.

### 2.3.1 Toolchain

The toolchain for designing specialized cores takes C programs as input, splits them into datapath and control segments, and then uses a state-of-the-art EDA tool flow to generate a circuit fully realizable in silicon. The toolchain also generates a cycle-accurate system simulator for the new hardware. The simulator provides performance measurements as well as generates traces that drive Synopsys VCS and PrimeTime simulation of the placed-and-routed netlist.

Figure 2.5 depicts the various stages of the toolchain. The toolchain is based on the OpenIMPACT (1.0rc4) [Ope], CodeSurfer (2.1p1) [Cod], and LLVM (2.4) [LA04] compiler infrastructures and accepts a large subset of the C language, including arbitrary pointer references, switch statements, and loops with complex conditions.

In the hotspot identification stage, functions or subregions of functions (e.g., key loops) are tagged for conversion into specialized cores based on profile information. The toolchain uses outlining to isolate the region and then uses exhaustive inlining to remove function calls. Also, the global variables are passed by reference as additional input arguments.

The C-to-Verilog stage generates the control and dataflow graphs for the function in SSA [CFR<sup>+</sup>89] form. This stage then adds basic blocks and control states for each memory operation and multi-cycle instruction. The final step of the C-to-Verilog stage generates synthesizeable Verilog for the specialized core. This requires converting  $\phi$  operators into muxes, inserting registers at the definition of each value, and adding self loops to the control flow graph for the multi-cycle operations. Then, it generates the control unit with a state machine that matches the control flow graph. This stage of the toolchain also generates a cycle-accurate module for our architectural simulator. The further details of this stage can be found in [VSG<sup>+</sup>10].

### 2.3.2 Simulation infrastructure

Our cycle-accurate simulation infrastructure is based on btl, the Raw simulator [TLM $^+$ 04]. The btl simulator was modified to model a cache-coherent memory

among multiple processors, to include a scan chain interface between the CPU and all of the local specialized cores, and to simulate the specialized logic itself.

### 2.3.3 Synthesis

For synthesis, the toolchain targets a TSMC 45 nm GS process using Synopsys Design Compiler (C-2009.06-SP2) and IC Compiler (C-2009.06-SP2). Our toolchain generates synthesizeable Verilog and automatically processes the design in the Synopsys CAD tool flow, starting with netlist generation and continuing through placement, clock tree synthesis, and routing, before performing post-route optimizations.

### 2.3.4 Power measurements

In order to measure the power usage of specialized cores, the btl simulator periodically samples execution by storing traces of all inputs and outputs to the specialized logic. Each sample starts with a "snapshot" recording the entire register state of the specialized core and continues for 10,000 cycles. The current sampling policy is to sample 10,000 out of every 50,000 cycles, and we discard sampling periods corresponding to the initialization phase of the application.

The power measurement stage feeds each trace sample into the Synopsys VCS (C-2009.06) logic simulator. Along with the Verilog code our toolchain also automatically generates a Verilog testbench module, which initiates the simulation of each sample by scanning in the register values from each trace snapshot. The VCS simulation generates a VCD activity file, which we pipe as input into Synopsys PrimeTime (C-2009.06-SP2). PrimeTime computes both the static and dynamic power for each sampling period.

To model power for other system components, this stage uses processor and clock power values from specifications for a MIPS 24KE processor in TSMC 90 nm and 65 nm processes [MIP09], and component ratios for Raw reported in [KTMW03], scaled to a 45 nm process. For its measurements, this stage assumes a MIPS core frequency of 1.5 GHz with 0.077 mW/MHz for average CPU operation.

Finally, this stage uses CACTI 5.3 [TMAJ08] for I- and D-cache power.

#### Acknowledgments

Portions of this research were funded by the US National Science Foundation under NSF CAREER Awards 06483880 and 0846152, and under NSF CCF Award 0811794.

This chapter contains material from "Conservation cores: reducing the energy of mature computations", by Ganesh Venkatesh, Jack Sampson, Nathan Goulding, Saturnino Garcia, Vladyslav Bryksin, Jose Lugo-Martinez, Steven Swanson and Michael Bedford Taylor, which appears in ASPLOS '10: Proceedings of the fifteenth edition of ASPLOS on Architectural support for programming languages and operating systems. The dissertation author was the primary investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page in print or the first screen in digital media. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or email permissions@acm.org.

#### Chapter 3

### Patchable Conservation Cores: Energy-efficient circuits with processor-like lifetimes

Chapter 1 explains the utilization wall phenomenon and the challenges it presents in effectively using the increasing transistor counts to scale performance. The previous chapter described the Arsenal system, a massively heterogeneous tiled architecture that seeks to scale performance in spite of the utilization wall by synthesizing application-specific circuits targeting the key functions of the system workload. These application-specific circuits provide energy-efficient execution of irregular integer codes and can improve the energy efficiency by up to 30X compared to an efficient in-order MIPS processor [TLM+04]. These specialized circuits enable the Arsenal system to optimize energy-per-computation, which translates into better system performance by allowing more computations to run in parallel.

However, these application-specific circuits are very tightly coupled to the source code they target and cannot support any change in the same. Hence, these circuits are tied to the version of the application they were designed for and cannot support older or newer application versions. This lack of flexibility makes these application-specific circuits poor candidates for many of the applications in a system's workload. From a system designer's standpoint, designing co-processors that can only target a particular version of an application can cause two main prob-

lems – these specialized circuits would become unusable as soon as the application version is upgraded and also, circuits targeting the latest version will provide little benefit to the users still using the older application versions.

To address these issues, this thesis proposes Patchable Conservation cores (C-cores), application-specific circuits that remain useful across application versions, providing them with lifetimes comparable to those of general-purpose processors. The main contribution of this work is the novel *patching* mechanism that provides these application-specific circuits with targeted reconfigurability to enable them to support multiple application versions. This work extends the toolchain presented in the previous section to generate configuration "patches" corresponding to different application versions. At runtime, the c-core utilizes the configuration patch to adapt to the application version that wants to run on it. In this manner, c-cores remain useful across application versions, providing them with lifetimes comparable to that of a general-purpose processor.

This chapter is organized as follows. Section 3.1 motivates the need for reconfigurability in application-specific circuits. Section 3.2 describes the reconfigurability mechanisms that this work proposes to improve the longevity of these specialized circuits. Section 3.3 explains that patching algorithm for mapping alternate application versions onto a patchable c-core. Section 3.4 presents the methodology for designing and configuring the patchable c-cores. Section 3.5 evaluates the energy efficiency and longevity of patchable c-cores. Section 3.6 analyzes the area and energy overheads of the reconfigurability mechanisms and proposes optimizations to mitigate them without affecting the c-core's longevity. Section 3.7 proposes a mechanism to further improve the backward compatibility of the patchable c-cores. Section 3.8 concludes this chapter.

#### 3.1 Case for Reconfigurability in Application Specific Circuits

This work seeks to provide energy-efficient execution for *mature* applications, applications that have a relatively stable set of core functions. While the code

base of these applications will change across versions, the source code corresponding to the core functionality changes very infrequently, and when it does change, the changes tend to be relatively minor. This section analyzes the changes in the core functions of mature applications across successive versions and uses that analysis to motivate the need for providing targeted reconfigurability in application-specific circuits.

To better understand how the core functions change in mature applications, this section analyzes the changes across successive versions of DJPEG, CJPEG, Libpng, Sat Solver, MCF, VPR, and Bzip2 and documents the code change patterns that were commonly seen. Figure 3.1 shows the commonly seen code change pattern. The analysis shows that supporting these changes would allow the application-specific circuits to adapt to multiple versions of the applications listed above, potentially enabling these configurable circuits to remain useful for eight years on average. These commonly seen source code change patterns are summarized below.

Control flow changes A commonly seen change in the key functions is the addition or removal of certain computations. Figure 3.1(a) shows the changes in the function refresh\_potential across versions SPEC2000 and SPEC2006 of MCF. The main change across the two versions is the removal of a for loop in the beginning of the function, and the rest of the function code remains the same.

Changes in datapath operators and constants The second kind of common change patterns includes changes in expression constants and changes in datapath operators such as loop termination conditions (< replaced by  $\le$ ). Figure 3.1(b) shows the changes in the function sentMTFValues across versions 1.0.2 and 1.0.3 of Bzip2. The only change across the two versions is in the constant value used to ensure that a program variable value lies within the valid range.

Changes in the memory layout Another form of commonly seen change is in the layout of the program data structures. These changes include addition, deletion or rearrangement of structure fields. Figure 3.1(c) shows the changes in the data

```

long refresh_potential( network_t *net )

long refresh_potential( network_t *net )

node_t *stop = net->stop_nodes;

node_t *node, *tmp;

node_t *root = net->nodes;

node_t *node, *tmp;

node_t *root = net->nodes;

long checksum = 0;

long checksum = 0;

for( node = root, stop = net->stop_nodes;

node < (node_t*)stop; node++ )</pre>

node->mark = 0;

root->potential = (cost_t) -MAX_ART_COST;

tmp = node = root->child;

root->potential = (cost_t) -MAX_ART_COST;

tmp = node = root->child;

while( node != root )

while( node != root )

return checksum;

return checksum;

MCF SPEC2000

MCF SPEC2006

(a)

void sendMTFValues(Estate *s){

void sendMTFValues(Estate *s){

/*--- Assign actual codes for the tables. --*/

-- Assign actual codes for the tables. --*/

for (t = 0; t < nGroups; t++) {

for (t = 0; t < nGroups; t++) {

minLen = 32;

minLen = 32;

maxLen = 0;

for (i = 0; i < alphaSize; i++) {

maxLen = 0;

for (i = 0; i < alphaSize; i++) {

\begin{array}{l} \mbox{if (s->len[t][i] > maxLen) maxLen = s->len[t][i];} \\ \mbox{if (s->len[t][i] < minLen) minLen = s->len[t][i];} \\ \end{array}

\begin{array}{l} \mbox{if (s->len[t][i] > maxLen) maxLen = s->len[t][i];} \\ \mbox{if (s->len[t][i] < minLen) minLen = s->len[t][i];} \\ \end{array}

AssertH (!(maxLen > 20), 3004);

AssertH (!(maxLen > 17 /*20*/), 3004);

AssertH (!(minLen < 1), 3005);

BZ2_hbAssignCodes (&(s->code[t][0]), &(s->len[t][0]),

AssertH (!(minLen < 1), 3005);

BZ2_hbAssignCodes (&(s->code[t][0]), &(s->len[t][0]),

minLen, maxLen, alphaSize );

minLen, maxLen, alphaSize);

}

BZIP2 v1.0.2

BZIP2 v1.0.3

(b)

struct jpeg_decompress_struct {

struct jpeg_decompress_struct {

struct jpeg_source_mgr * src;

struct jpeg_source_mgr * src;

JDIMENSION image_width;

JDIMENSION image_width;

JDIMENSION image_height;

JDIMENSION image_height;

double output_gamma;

double output_gamma;

boolean buffered_image;

boolean raw_data_out;

J DCT METHOD dct method:

boolean do_fancy_upsampling;

boolean do_block_smoothing;

boolean quantize_colors;

boolean quantize_colors;

DJPEG v5

DJPEG v6

(c)

```

Figure 3.1: Commonly seen source code modification patterns across application versions The figure shows changes across versions of a) MCF, b) Bzip2, and c) DJPEG. The changes are shown in bold.

structure jpeg\_decompress\_struct across versions 5.0 and 6.0 of DJPEG. The data structure's member variables are reorganized and new variables are added (for ex. buffered\_image). While the source of the hot spot functions in DJPEG does not change across versions, the change in the data structure layout changes the offsets used to calculate the memory addresses for load/store operations.

The above analysis shows that while the source code for the key functions might change across application versions, the majority of the code in a key function tends to remain the same. Hence, across application versions, hardware implementation is available for the majority of the code in a key function and the new version should ideally be able to reuse the available hardware, albeit at a lower level of performance/energy efficiency.

# 3.2 Reconfigurability support in Conservation Cores

The analysis of successive application versions, presented in the previous section, revealed a number of common change patterns, all of which were relatively minor changes in source code. As discussed in Section 2.2.1, the c-core control unit and datapath very closely correspond to the program structure. Hence, the changes in c-core hardware design would mirror the changes in the source code. Fortunately, c-cores can support many of these changes effectively with very modest amounts of reconfigurability. This thesis proposes the following three patching mechanisms for adjusting the c-core behavior after they have been fabricated.

Configurable constants The first patching mechanism generalizes hard-coded immediate values into configurable registers. This mechanism supports changes to the values of compile-time constants and the insertion, deletion, or rearrangement of structure fields.

Generalized single-cycle datapath operators To support the replacement of one operator with another, the second patching mechanism generalizes any addition or subtraction to an adder-subtractor, any comparison operation to a generalized comparator, and any bitwise operation to a bitwise ALU. A small configuration register is then added for each such operator, determining which operation is currently active.

Control flow changes In order to handle changes in the CFG's structure and changes to basic blocks that go beyond what the above mechanisms can handle, the third patching mechanism provides a flexible exception mechanism. The control path contains a bit for each state transition that determines whether the c-core should treat it as an exception.

When the state machine makes an exceptional transition, the c-core stops executing and transfers control to the general-purpose core. The exception handler extracts current variable values from the c-core via the scan-chain-based interface, performs a portion of the patched execution, transfers new values back into the c-core, and resumes execution. The exception handler can restart c-core execution at any point in the CFG, so exceptions can arbitrarily alter control flow and/or replace arbitrary portions of the CFG.

The next section describes the patch generation algorithm for mapping the newer application versions onto a patchable c-core. The patching algorithm utilizes this mapping to determine the reconfiguration state necessary to allow a c-core to continue to run code even after it has been changed from the version used to generate that c-core.

#### 3.3 Patching Algorithm

This section describes the patching algorithm this thesis proposes. The patching algorithm works directly on the program's dataflow and control flow graph, a representation that can be generated from either source code or a compiled binary. This enables the patch generation to happen at assembly level, allowing the new application versions to run on the specialized hardware without any source code modifications.

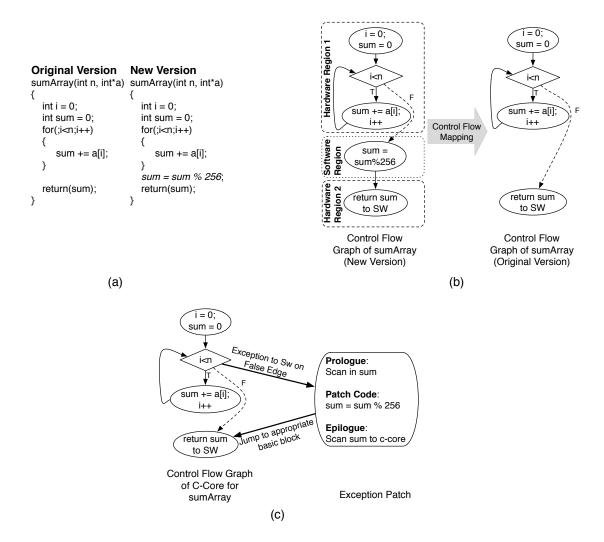

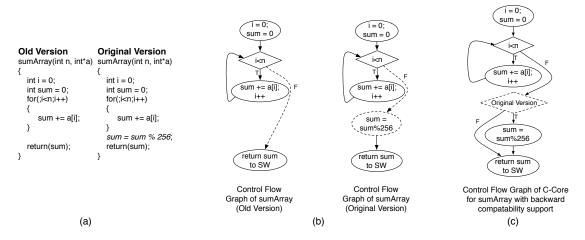

Figure 3.2: **Handling changes in control flow across versions** (a) The original and new source for sumArray() is shown. (b) The mapping between the new and the original version of sumArray's CFG covers most of the target version in two hardware regions. (c) Transfers of control between the hardware and software regions require an exception.

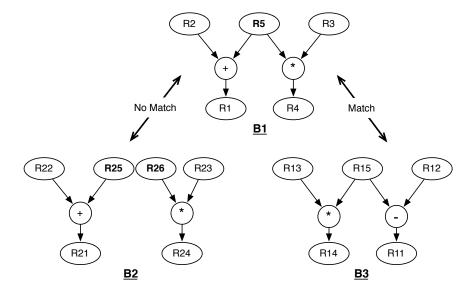

Figure 3.3: **Basic block matching** Target block B3 can be mapped onto the hardware for original block B1, but target block B2 does not match B1 and cannot be mapped: There is no consistent mapping between the register names in bold.

When a c-core-equipped processor ships, it can run the latest version, referred to as the *original* version, of the targeted applications without modification. When a new version of an application becomes available, the patching algorithm determines how to map the new version of the software, referred to as the *target* version, onto the existing c-core hardware. The goal of the patching process is to generate a *patch* for the original hardware that will let it run the target software version.

The patching algorithm proceeds in four stages: basic block mapping, control flow mapping, register remapping, and patch generation.

#### 3.3.1 Basic block mapping

The first stage of the algorithm identifies which hardware basic blocks in the original hardware can run each basic block in the target application. Since the original hardware includes generalized arithmetic operators and configurable constant registers, there is significant flexibility in what it means for two basic blocks to *match*. Two basic blocks match if the following conditions are true.

- The basic blocks have the same number of instructions, not including unconditional jumps (which only affect the control path and, therefore, have no effect on the generated hardware).

- The data flow graphs of the two basic blocks are isomorphic up to operators at the nodes and constant values.

- For each instruction in the target basic block, there is a corresponding instruction in the original that it is compatible with. That is, the original instruction is either identical to the target, or can be patched to turn it into the target instruction.

Figure 3.3 shows one original block, B1 and two target blocks, B2 and B3. The mapping process will mark B3 as a possible match for B1, and B2 as not matching B1.

#### 3.3.2 Control flow mapping

The next step of the patching algorithm is building a map between the control flow graphs of the original and target versions. This step identifies regions of the target control flow graph that map perfectly onto disjoint portions of the original hardware. These portions of the function are called *hardware regions*, and they will execute entirely in hardware under the patch. Ideally, all basic blocks in the target will map to basic blocks in the original, and there will be a single hardware region. In practice this will sometimes not be possible. The target version may have basic blocks inserted or deleted relative to the original, or one of the basic blocks may have changed enough that no matching basic block exists in the original. The exception mechanism executes the remaining, unmapped software regions on the general purpose processor.

To divide the control flow graph, the algorithm starts by matching the entry node of the target graph with the entry of the original graph. The algorithm proceeds with a breadth-first traversal of the target graph, greedily adding as many blocks to the hardware region as possible. When the hardware region can grow no larger, the region is complete.

A region stops growing for one of two reasons: It may reach the end of the function or run up against another hardware region. Alternatively, there may be no matching basic blocks available to add to the region because of a code modification. In that case, the patching algorithm marks the non-matching basic blocks as part of the software region and selects the lowest depth matching basic block available to seed the creation of a new hardware region. This stage of the algorithm terminates when the entire function has been partitioned into hardware regions and software regions.

Figure 3.2 illustrates this portion of the algorithm. Figure 3.2(a) shows the original software version of a function called sumArray() and its CFG. Figure 3.2(b) shows the target version of sumArray() which has an extra operation. Most of the new sumArray() is mapped onto the original c-core in two hardware regions, but the new operation is mapped to a separate software region because the hardware for it does not exist in the original c-core. Any transition to this region will be marked as an exception.

#### 3.3.3 Register mapping

The next phase of the algorithm generates a consistent local mapping between registers in the original and target basic block for each matched basic block pair. In this mapping, the output of the first instruction in the original basic block corresponds to the output of the first instruction in the target basic block, and so on.