|

- Evaluating Ruche Networks: Physically Scalable, Cost-Effective, Bandwidth-Flexible NoCs

Dai Cheol Jung and Michael Taylor. In ISCA 2025 (pdf)(pdf).

- ZynqParrot: A Scale-Down Approach to Cycle-Accurate, FPGA-Accelerated Co-Emulation

Daniel Ruelas-Petrisko, Farzam Gilani, Anoop Mysore Nataraja, Zoe Taylor, Michael Taylor. In Arxiv.org 2025 (pdf).

- ReaLLM: A Trace-Driven Framework for Rapid Simulation of Large-Scale LLM Inference

Huwan Peng, Scott Davidson, C.-J. Richard Shi and Michael Taylor. In ASAP 2025 (pdf).

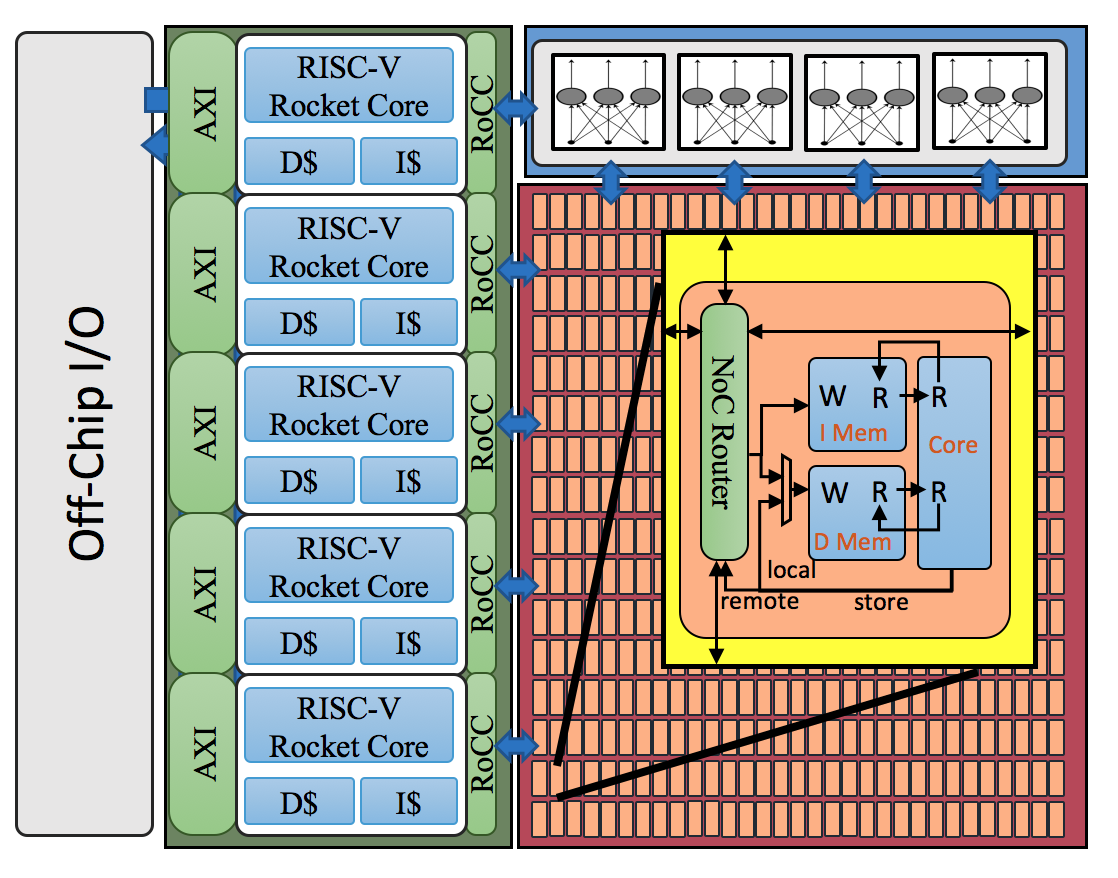

- Scalable, Programmable and Dense: The HammerBlade Open-Source RISC-V Manycore

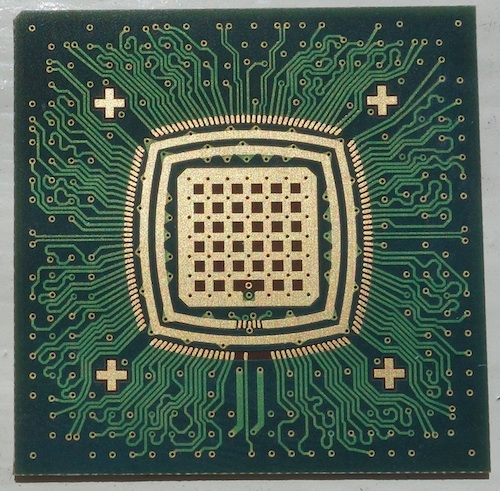

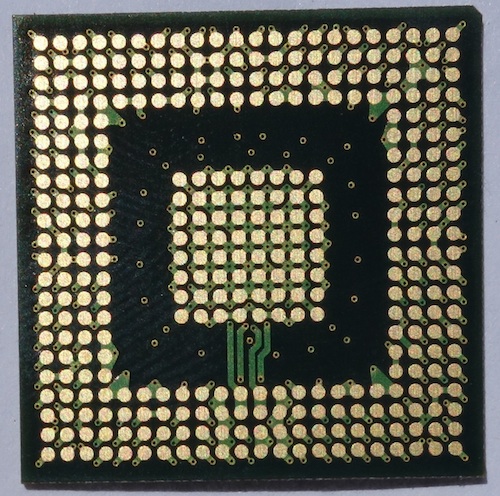

Dai Cheol Jung, Max Ruttenberg, Paul Gao, Scott Davidson, Daniel Petrisko, Kangli Li, Aditya K Kamath, Lin Cheng, Shaolin Xie, Peitian Pan, Zhongyuan Zhao, Zichao Yue, Bandhav Veluri, Sripathi Muralitharan, Adrian Sampson, Andrew Lumsdaine, Zhiru Zhang, Christopher Batten, Mark Oskin, Dustin Richmond and Michael Bedford Taylor

in ISCA 2024. (pdf) (bib)

- RETROSPECTIVE: ASIC Clouds: Specializing the Datacenter

by Michael Taylor.

in ISCA@50 Retrospective: 1996-2020, June 2023 (pdf)

- RETROSPECTIVE: Evaluation of the RAW Microprocessor: An Exposed-Wire-Delay Architecture for ILP and Streams

by Michael Taylor, David Wentzlaff, Saman Amarasinghe and Anant Agarwal.

in ISCA@50 Retrospective: 1996-2020, June 2023 (pdf)

- RISE: RISC-V SoC for En/Decryption Acceleration on the Edge for Homomorphic Encryption

by Zahra Azad, Guowei Yang, Rashmi Agrawal, Daniel Petrisko, Michael Taylor and Ajay Joshi.

in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Volume 31, Issue 10, July 2023. (bib)

- Chiplet Cloud: Building AI Supercomputers for Serving Large Generative Models

by Huwan Peng, Scott Davidson, Richard Shi, Shuaiwen Leon Song, Michael Taylor. July 2023.

in arxiv.org (arxiv link)

- Beyond Static Parallel Loops: Supporting Dynamic Task Parallelism on Manycore Architectures with Software-Managed Scratchpad Memories

Lin Cheng, Max Ruttenberg, Dai Cheol Jung, Dustin Richmond, Michael Taylor, Mark Oskin, and Christopher Batten.

in ASPLOS 2023. (bib) (YouTube) (pdf).

- ProcessorFuzz: Processor Fuzzing with Control and Status Registers Guidance

Sadullah Canakci, Chathura Rajapaksha, Leila Delshadtehrani, Anoop Nataraja, Michael Bedford Taylor, Manuel Egele, and Ajay Joshi.

in HOST 2023. (bib) (pdf) Best Paper Award.

- NeuriCam: Key-Frame Video Super-Resolution and Colorization for IoT Cameras

Bandhav Veluri and Collin Pernu and Ali Saffari and Joshua Smith and Michael Taylor and Shyam Gollakota.

in Mobicom 2023. (bib)(arxiv link)

- bsg_tag: A Minimal Open-Source ASIC Configuration System

Daniel Petrisko, Paul Gao, Michael Taylor.

in Latch-Up 2023. (Slides) (Video)

- The BlackParrot BedRock Cache Coherence System

Mark Wyse, Daniel Petrisko, Farzam Gilani, Yuan-Mao Chueh, Paul Gao, Dai Cheol Jung, Sripathi Muralitharan, Shashank Vijaya Ranga, Mark Oskin, and Michael Taylor.

arxiv.org. November 2022.

- RACE: RISC-V SoC for En/decryption ACceleration on the Edge for Homomorphic Computation.

Z. Azad, G. Yang, R. Agrawal, D. Petrisko, M. Taylor and A. Joshi.

in ISLPED 2022. (bib)(pdf)

- A Tensor Processing Framework for CPU-Manycore Heterogeneous Systems.

Lin Cheng, Peitian Pan, Zhongyuan Zhao, Krithik Ranjan, Jack Weber, Bandhav Veluri, Borna Ehsani, Max Ruttenberg,

Dai Cheol Jung, Preslav Ivanov, Dustin Richmond, Michael Taylor, Zhiru Zhang, and Christopher Batten.

In IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems (TCAD), 41(6):1620–1635, June 2022.

(bib)(pdf)

- DirectFuzz: Automated Test Generation for RTL Designs using Directed Graybox Fuzzing.

Sadullah Canakci, Leila Delshadtehrani, Furkan Eris, Michael Bedford Taylor, Manuel Egele, and Ajay Joshi.

in DAC 2021. (pdf) (bib)

- Taming the Zoo: A Unified Graph Compiler Framework for Novel Architectures.

Ajay Brahmakshatriya, Emily Furst, Victor Ying, Claire Hsu, Max Ruttenberg, Yunming Zhang, Tommy Jung, Dustin Richmond, Michael Taylor, Julian Shun, Mark Oskin, Daniel Sanchez, Saman Amarasinghe.

in ISCA 2021. (pdf) (bib)

- η-LSTM: Co-Designing Highly-Efficient Large LSTM Training

via Exploiting Memory-Saving and Architectural Design

Opportunities.

Xingyao Zhang, Haojun Xia, Donglin Zhuang, Hao Sun, Xin Fu, Michael Taylor, Shuaiwen Leon Song.

in ISCA 2021. (pdf) (pptx) (bib)

- Q-VR: System-Level Design for Future Mobile Collaborative Virtual Reality.

Chenhao Xie, Xie Li, Yang Hu, Huwan Peng, Michael Taylor and Shuaiwen Leon Song.

in ASPLOS 2021. (pdf) (bib)

- NoC Symbiosis.

Daniel Petrisko, Chun Zhao, Scott Davidson, Paul Gao, Dustin Richmond and Michael Bedford Taylor.

in NOCS 2020.

(pdf) (pptx) (bib)

- Ruche Networks: Wire-Maximal, No-Fuss NoCs.

Dai Cheol Jung, Scott Davidson, Chun Zhao, Dustin Richmond, Michael Bedford Taylor.

in NOCS 2020.

(pdf) (pptx) (bib)

- Your agile open source HW stinks (because it is not a system).

Michael Bedford Taylor

in ICCAD 2020. (pdf) (bib)

- BaseJump STL: A Standard Template Library for Hardware Design

Daniel Petrisko, Michael Taylor

in Latch-Up 2019. (Slides) (< href="https://youtu.be/7MsS3d81Wdw?si=Jvs6ZC6Kjz2kf2XO">Video

- ASIC Clouds: Specializing the Datacenter for Planet-Scale Applications. Michael Bedford Taylor, Luis Vega, Moein Khazraee, Ikuo Magaki, Scott Davidson, Dustin Richmond. In Communications of the ACM, July 2020. (pdf)(bib)

- BlackParrot: An Agile Open-Source RISC-V Multicore for Accelerator SoCs. Daniel Petrisko, Farzam Gilani, Mark Wyse, Dai Cheol Jung, Scott Davidson, Paul Gao, Chun Zhao, Zahra Azad, Sadullah Canakci, Bandhav Veluri, Tavio Guarino, Ajay Joshi, Mark Oskin and Michael Bedford Taylor. In IEEE Micro, July/August 2020. (pdf)(bib)(< href="https://archive.fosdem.org/2020/schedule/event/riscv_blackparrot">Talk (FOSDEM 2020)

- A 7.3 M Output Non-Zeros/J, 11.7 M Output Non-Zeros/GB Reconfigurable Sparse Matrix-Matrix Multiplication Accelerator. Dong-Hyeon Park, Subhankar Pal, Siying Feng, Paul Gao, Jielun Tan, Austin Rovinski, Shaolin Xie, Chun Zhao, Aprova Amarnath, Jonathan Beaumont, Kuan-Yu Chen, Chaitali Chakrabarti, Michael Bedford Taylor, Trevor Mudge, David Blauuw, Hun-Seok Kim, Ronald Dreslinski. In Journal of Solid State Circuits, April 2020. (pdf)(bib)

- Evaluating Celerity: A 16nm 695 Giga-RISC-V Instructions/s Manycore Processor with Synthesizeable PLL. Austin Rovinski, Chun Zhao, Khalid Al-Hawaj, Paul Gao, Shaolin Xie, Christopher Torng, Scott Davidson, Aporva Amarnath, Luis Vega, Bandhav Veluri, Anuj Rao, Tutu Ajayi, Julian Puscar, Steve Dai, Ritchie Zhao, Dustin Richmond, Zhiru Zhang, Ian Galton, Christopher Batten, Michael B. Taylor, Ronald G. Dreslinski. In IEEE Solid State Circuits Letters, December 2019. (pdf) (bib)

- Technical perspective: Bootstrapping a future of open source, specialized hardware. Communications of the ACM 62(16):78 (2019).

- A 7.3 M Output Non-Zeros/J Sparse Matrix-Matrix Multiplication Accelerator Using Memory Reconfiguration in 40 nm.

Pal, D.-H. Park, S. Feng, P. Gao, J. Tan, A. Rovinski, S. Xie, C. Zhao, A. Amarnath, M. Taylor, T. Mudge, D. Blaauw,

H.-S. Kim, R. Dreslinski, T. Wesley, J. Beaumont, K.-Y. Chen and C. Chakrabarti. In Symposium on VLSI Circuits, June 2019.

(bib)

- A 1.4 GHz 695 Giga RISC-V Inst/s 496-core Manycore Processor with Mesh On-Chip Network and an All-Digital

Synthesized PLL in 16nm CMOS.

A. Rovinski, C. Zhao, K. Al-Hawaj, P. Gao, S. Xie, C. Torng, S. Davidson, A.

Amarnath, L. Vega, B. Veluri, A. Rao, T. Ajayi, J. Puscar, S. Dai, R. Zhao, D. Richmond, Z. Zhang, I.

Galton, C. Batten, M. B. Taylor and R. G. Dreslinski. In Symposium on VLSI Circuits, June 2019. (pdf)

(bib)

- Extreme Datacenter Specialization for Planet-Scale Computing: ASIC Clouds.

Shaolin Xie, Scott Davidson, Ikuo Magaki, Moein Khazraee, Luis Vega, Lu Zhang, Michael B. Taylor. In ACM SIGOPS Operating System Review, July 2018. (bib)

- The Celerity Open-Source 511-Core RISC-V Tiered Accelerator Fabric.

by Scott Davidson, Shaolin Xie, Chris Torng, Khalid Al-Hawaj, Austin Rovinski, Tuto Ajayi, Luis Vega, Chun Zhao, Ritchie Zhao, Steve Dai, Aporva Amarnath, Bandhav Veluri, Paul Gao, Anuj Rao, Gai Liu, Rajesh K. Gupta, Zhiru Zhang, Ronald Dreslinski, Christopher Batten, Michael Bedford Taylor.

IEEE Micro, March/April 2018. (pdf)(bib)

- BaseJump STL: SystemVerilog needs a Standard Template Library for Hardware Design.

Michael B. Taylor.

Design Automation Conference (DAC), June 2018. (pdf)(bib)(talk)

- Hiding Intermittent Information Leakage with Architectural Support for Blinking.

by Alric Althoff, Joseph McMahan, Luis Vega, Scott Davidson, Timothy Sherwood, Michael Taylor, and Ryan Kastner.

International Symposium on Computer Architecture (ISCA), June 2018.(bib)(pdf)

- Open Source Hardware: Stone Soups and Not Stone Statues, Please.

by Hadi Esmaeilzadeh and Michael Bedford Taylor.

SIGARCH Computer Architecture Today, Dec 2017.(pdf)(bib)

- The Evolution of Bitcoin Hardware.

This is a great overview of Bitcoin mining hardware evolution, a follow-on to Taylor's CASES 2013 paper, it updates that groundbreaking paper to 2017.

Michael Bedford Taylor.

IEEE Computer, Sept 2017.(pdf)(bib)

- Celerity: An Open Source 511-core RISC-V Tiered Accelerator Fabric.

Ritchie Zhao, Chun Zhao, Shaolin Xie,Bandhav Veluri,Luis Vega, Christopher Torng,

Ningxiao Sun, Austin Rovinski,Anuj Rao,Gai Liu,Paul Gao,Scott Davidson,

Steve Dai, Aporva Amarnath, KhalidAl-Hawaj, Tutu Ajayi

Christopher Batten, Ronald G. Dreslinski,

Rajesh K.Gupta, Michael B.Taylor, Zhiru Zhang.

Proceedings of the 7th RISC-V Workshop, Milpitas, CA. November 2017. (Slides)(

Video)

(bib)

- Celerity: An Open Source RISC-V Tiered Accelerator Fabric.

This is an overview of our Tiered Accelerator Fabric architecture, and of a 511-core RISC-V implementation in 16 nm, including 5 Linux-capable RISC-V cores, 496-core RISC-V manycore, and a binarized neural network.

Tutu Ajayi, Khalid Al-Hawaj, Aporva Amarnath, Steve Dai, Scott Davidson,

Paul Gao, Gai Liu, Atieh Lotfi, Julian Puscar, Anuj Rao, Austin Rovinski,

Loai Salem, Ningxiao Sun, Christopher Torng, Luis Vega, Bandhav Veluri, Xiaoyang Wang,

Shaolin Xie, Chun Zhao, Ritchie Zhao, Christopher Batten, Ronald G. Dreslinski, Ian Galton, Rajesh K. Gupta,

Patrick P. Mercier, Mani Srivastava, Michael Bedford Taylor and Zhiru Zhang.

Proceedings of Hotchips, 2017. (pdf)(bib)

- Experiences Using the RISC-V Ecosystem to Design an Accelerator-Centric SoC in TSMC 16nm.

Has more details on the open source code for Celerity.

Proceedings of CARRV, October 2017. (pdf) (slides)

- RV-IOV: Tethering RISC-V Processors via Scalable I/O Virtualization

Details on our I/O Virtualization system for Celerity and RISC-V.

Luis Vega and Michael Bedford Taylor.

Proceedings of CARRV, October 2017. (pdf) (slides) (bib)

- Specializing a Planet's Computation: ASIC Clouds

Read this to get a great overview of ASIC Clouds.

Moein Khazraee, Luis Vega, Ikuo Magaki and Michael Bedford Taylor.

IEEE Micro May/June 2017.

(pdf)(bib)

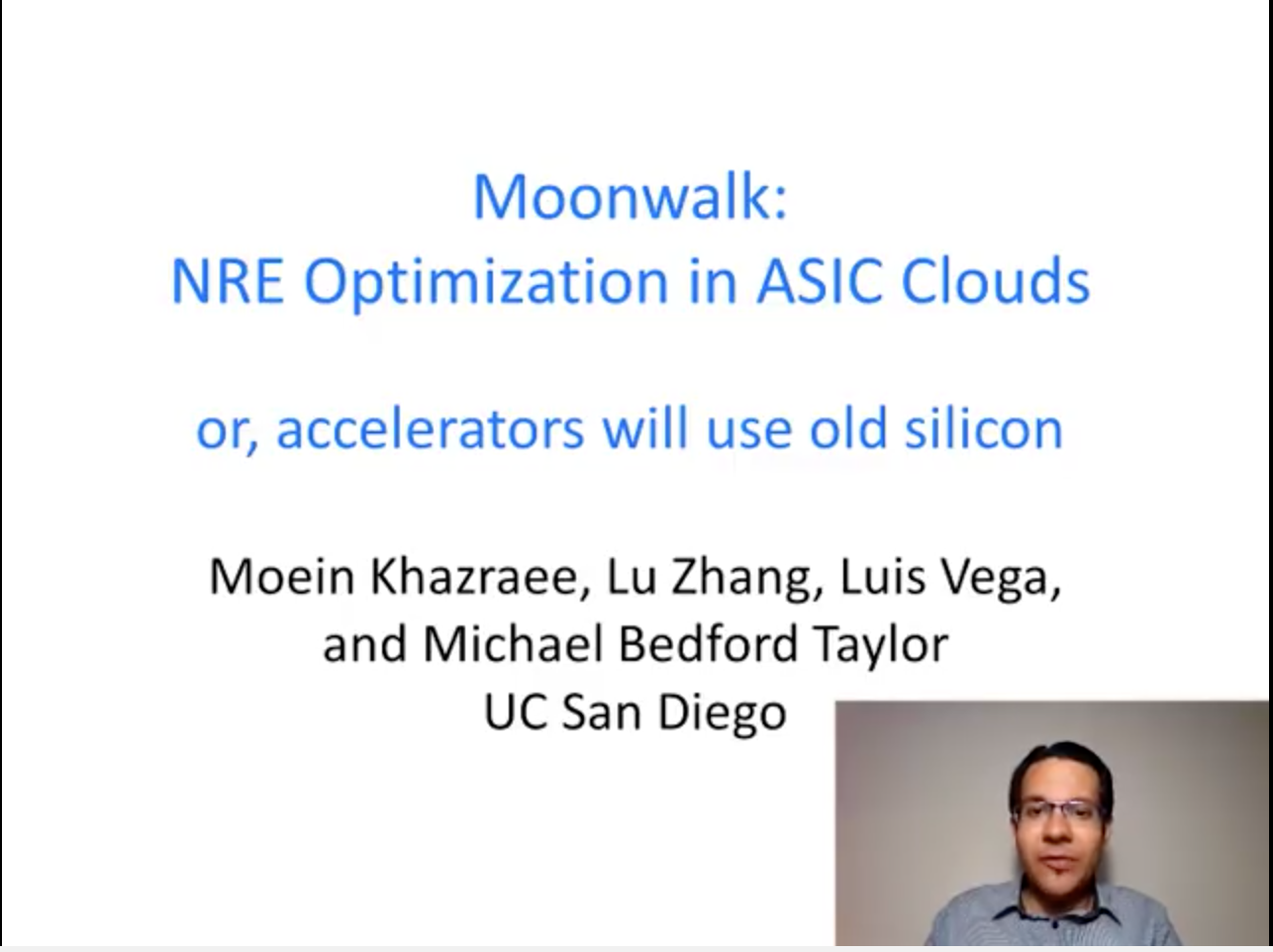

- Moonwalk: NRE Optimization in ASIC Clouds or, accelerators will use old silicon

Moein Khazraee, Lu Zhang, Luis Vega, and Michael Bedford Taylor, in ASPLOS 2017.

(pdf) (ASPLOS 2017 talk) (bib) (talk).

- Geocomputers and the Commercial Borg

Michael Bedford Taylor.

SIGARCH Computer Architecture Today, Mar 2017.(pdf)(bib)

- ASIC Clouds: Specializing the Datacenter

Ikuo Magaki, Moein Khazraee, Luis Vega Gutierrez, and Michael Bedford Taylor.

International Symposium on Computer Architecture (ISCA), June 2016. (pdf) (bib)

- Power Side Channels in Security ICs: Hardware Countermeasures

Lu Zhang, Luis Vega, Michael Taylor

arxiv.org, May 2016. (pdf)

- CortexSuite: A Synthetic Brain Benchmark Suite

Shelby Thomas, Chetan Gohkale, Enrico Tanuwidjaja, Tony Chong, David Lau, Saturnino Garcia, and Michael Bedford Taylor.

IEEE International Symposium on Workload Characterization (IISWC), Oct 2014. (pdf) (bib)

- BlackBox: Lightweight Security Monitoring for COTS Binaries

(with accepted artifact!)

Byron Hawkins, Brian Demsky, and Michael Bedford Taylor.

Code Generation and Optimization (CGO), February 2016. (pdf) (bib)

- A Runtime Approach to Security and Privacy

Byron Hawkins, Brian Demsky, and Michael Bedford Taylor.

European Security and Privacy, March 2016. (pdf) (bib)

- A Landscape of the New Dark Silicon Design Regime

Michael Taylor.

IEEE Micro, Sep/Oct 2013. (pdf) (bib)

Conference Presentations:

Third Berkeley Symposium on Energy Efficient Electronic Systems (E3S), October 2013. (pdf)(youtube)

Design Automation and Test in Europe (DATE), April 2014. (pdf)

- Bitcoin and The Age of Bespoke Silicon

Michael Bedford Taylor.

International Conference on Compilers, Architecture and Synthesis for Embedded Systems (CASES), Sept 2013. (Talk) (Paper)(bib)

- Exploring Energy Scalability in Coprocessor-Dominated Architectures for Dark Silicon

Qiaoshi Zheng, Nathan Goulding-Hotta, Scott Ricketts,

Steven Swanson, Michael Bedford Taylor, and Jack Sampson

Transactions on Embedded Computing Systems, March 2014. (paper) (bib)

- Quality Time: A Simple Online Technique for Quantifying Multicore Execution Efficiency

Anshuman Gupta, Jack Sampson, and Michael Bedford Taylor.

International Symposium on Performance Analysis of Systems and Software (ISPASS), March 2014. (pdf) (bib)

- DR-SNUCA: An Energy-Scalable Dynamically Partitioned Cache

Anshuman Gupta, Jack Sampson, Michael B. Taylor.

International Conference on Computer Design (ICCD), October 2013. (Talk) (Paper)(bib)

- Time Cube: A Manycore Embedded Processor with Interference-Agnostic Progress Tracking

Anshuman Gupta, Jack Sampson, Michael B. Taylor.

International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS), July 2013. (Talk) (Paper)(bib)

- Skadu: Efficient Vector Shadow Memories for Poly-Scopic

Program Analysis

Donghwan Jeon, Saturnino Garcia, and Michael B. Taylor.

Code Generation and Optimization (CGO), February 2013. (Talk) (Paper)(bib)

- Is Dark Silicon Useful?

Harnessing the Four Horsemen of the Coming Dark Silicon Apocalypse

Michael B. Taylor

Design Automation Conference (DAC), June 2012. (pdf) (bib) (slides).

Also Presented at:

ISCA's Dark Silicon Workshop (DaSi 2012)

ICCAD's Workshop on Domain-Specific Multicore Computing (2012).

- The Kremlin Oracle for Sequential Code Parallelization

Saturnino Garcia, Donghwan Jeon, Chris Louie, and Michael Bedford Taylor.

IEEE Micro, July/Aug 2012. (pdf) (bib)

- Sichrome: Mobile web browsing in Hardware to save Energy

Vikram Bhatt, Nathan Goulding-Hotta, Qiaoshi Zheng, Jack Sampson, Steve Swanson, and Michael B. Taylor.

Dark Silicon Workshop, ISCA, 2012. (bib)

- GreenDroid: An Architecture for the Dark Silicon Age

Nathan Goulding-Hotta, Jack Sampson, Qiaoshi Zheng, Vikram Bhatt, Steven Swanson and Michael Bedford Taylor

Asia and South Pacific Design Automation Conference (ASPDAC), February 2012. (pdf) (bib) (slides)

- QsCores: Trading Dark Silicon for Scalable Energy Efficiency with Quasi-Specific Cores

Ganesh Venkatesh, John Sampson, Nathan Goulding-Hotta, Sravanthi Kota Venkata, Michael Bedford Taylor, and Steven Swanson

International Symposium on Microarchitecture (MICRO), December 2011. (pdf) (bib)

- Kismet: Parallel Speedup Estimates for Serial Programs

Donghwan Jeon, Saturnino Garcia, Chris Louie, and Michael Bedford Taylor.

Annual ACM SIGPLAN Conference on Object-Oriented Programming, Systems, Languages, and Applications (OOPSLA), October 2011. (pdf) (bib)

- An Evaluation of Selective Depipelining for FPGA-based Energy-Reducing Irregular Code Coprocessors.

Jack Sampson, Manish Arora, Nathan Goulding-Hotta, Ganesh Venkatesh, Jonathan Babb, Vikram Bhatt, Michael Bedford Taylor and Steven Swanson.

Conference on Field Programmable Logic and Applications (FPL), September 2011. (pdf) (bib)

- The GreenDroid Mobile Application Processor: An Architecture for Silicon's Dark Future

Nathan Goulding-Hotta, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Auricchio, Po-Chao Huang, Manish Arora, Siddhartha Nath, Jonathan Babb,

Steven Swanson, and Michael Bedford Taylor.

IEEE Micro, March/April 2011. (pdf) (bib)

- Kremlin: Rebooting and Rethinking gprof for the Multicore Age

(aka Automatic Parallelism Planning and Discovery with Kremlin)

Saturnino Garcia, Donghwan Jeon, Chris Louie, and Michael Bedford Taylor.

Programming Language Design and Implementation (PLDI), June 2011. (pdf) (bib)

- Unifying manycore and FPGA processing with the RUSH Architecture

Brandon Beresini, Scott Ricketts, and Michael Bedford Taylor.

NASA/ESA Conference on Adaptive Hardware and Software Systems (AHS-2011), June 2011. (pdf)

- Conservation Cores: Energy-Saving Coprocessors for Nasty Real World Code

Jack Sampson, Ganesh Venkatesh, Nathan Goulding-Hotta, Saturnino

Garcia, Manish Arora, Siddhartha Nath, Vikram Bhatt, Steven Swanson,

and Michael Bedford Taylor.

Languages, Compilers, Tools and Theory for Embedded Systems (LCTES),

Research Highlights, Invited Talks, April 2011. (pdf)

- Greendroid: Exploring the next evolution in smartphone application processors

Steven Swanson and Michael Bedford Taylor.

Communications Magazine, IEEE 49(4):112 -119, April 2011. (pdf) (bib)

- Parkour: Parallel Speedup Estimates for Serial Programs

Donghwan Jeon, Saturnino Garcia, Chris Louie, Michael Bedford Taylor.

HOTPAR, June 2011. (pdf) (bib)

- Reducing the Energy Cost of Irregular Code Bases in Soft Processor Systems

Manish Arora, Jack Sampson, Nathan Goulding-Hotta, Jonathan Babb, Ganesh Venkatesh, Michael Bedford Taylor and Steven Swanson.

Field Customizable Computing Machines (FCCM), May 2011. (pdf) (bib)

- Kremlin: Like gprof, but for Parallelization

Donghwan Jeon, Saturnino Garcia, Chris Louie, Sravanthi Kota Venkata and Michael Bedford Taylor.

Principles and Practice of Parallel Programming (PPoPP), February 2011. (pdf, poster pdf) (bib)

- Efficient Complex Operators for Irregular Codes

Jack Sampson, Ganesh Venkatesh, Nathan Goulding-Hotta, Saturnino Garcia, Steven Swanson, and Michael Bedford Taylor.

High Performance Computer Architecture (HPCA), February 2011. (pdf) (bib)

- Bridging the Parallelization Gap: Automating Parallelism Discovery and Planning,

Saturnino Garcia, Donghwan Jeon, Chris Louie, Sravanthi Kota Venkata, Michael Bedford Taylor.

HOTPAR, June 2010. (pdf) (bib)

- GreenDroid: A Mobile Application Processor for a Future of Dark Silicon

Nathan Goulding, Jack Sampson, Ganesh Venkatesh, Saturnino Garcia, Joe Auricchio, Jonathan Babb, Michael Bedford Taylor and Steven Swanson.

HOTCHIPS, August 2010. (pdf) (talk ppt) (bib)(youtube)

- Conservation Cores: Reducing the Energy of Mature Computations.

Ganesh Venkatesh, John Sampson, Nathan Goulding, Saturnino Garcia, Slavik Bryskin, Jose Lugo-Martinez, Steven Swanson, and Michael Bedford Taylor.

Architectural Support for Programming Languages and Operating Systems (ASPLOS), March 2010. (pdf) (talk pdf, talk ppt) (bib)

- SD-VBS: The San Diego Vision Benchmark Suite.

Sravanthi Kota Venkata, Ikkjin Ahn, Donghwan Jeon, Anshuman Gupta, Christopher Louie, Saturnino Garcia, Serge Belongie, and Michael Bedford Taylor.

IEEE International Symposium on Workload Characterization (IISWC), October 2009. (pdf) (Download SD-VBS) (bib)

- Energy and Switch Area Optimizations for FPGA Global Routing Architectures

Yi Zhu, Yuanfang Hu, Michael B. Taylor, and Chung-Kuan Cheng

ACM Transactions on Design Automation of Electronic Systems (TODAES), January 2009.

(pdf) (bib)

- Tiled Multicore Processors.

Michael B. Taylor, Walter Lee, Jason E. Miller, David Wentzlaff, Ian Bratt, Ben Greenwald, Henry Hoffman, Paul R. Johnson, Jason S. Kim, James Psota, Arvind Saraf, Nathan Shnidman, Volker Strumpen, Matthew I. Frank, Saman Amarasinghe, and Anant Agarwal.

in Multicore Processors and Systems, Springer,

edited by Steve Keckler, Kunle Olukotun, and Peter Hofstee, 2009. (link)

- Advancing Supercomputer Performance Through Interconnection Topology Synthesis.

Yi Zhu, Michael Taylor, Scott B. Baden and Chung-Kuan Cheng

International Conference on Computer-Aided Design (ICCAD), November 2008. (pdf) (bib)

- Stream Multicore Processors.

Michael B Taylor, Walter Lee, Jason Eric Miller, David Wentzlaff,

Ian Bratt, Ben Greenwald, Henry Hoffmann, Paul Johnson,

Jason Kim, James Psota, Arvind Saraf, Nathan Shnidman,

Volker Strumpen, Matt Frank, Rodric Rabbah, Saman Amarasinghe, and

Anant Agarwal.

In Processor Design: System-on-chip

Computing for ASICs and FPGAs (hardcover)

Edited by Jari Nurmi (Editor), 2007. (link)

- FPGA Global Routing Architecture Optimization Using a Multicommodity Flow Approach.

Y. Hu, Y. Zhu, M.B. Taylor, and C.K. Cheng.

IEEE Int. Conf. on Computer Design (ICCD), pp. 144-151, 2007. (pdf) (bib)

- Runtime checking for program verification.

Karen Zee, Viktor Kuncak, Michael Taylor, and Martin Rinard.

7th International Workshop, RV 2007, Vancouver, Canada, March 13, 2007, Revised Selected Papers.

Lecture Notes on Computer Science, Springer Berlin, vol. 4839/2007, p. 202-213. (bib)

- Tiled Microprocessors.

Michael B Taylor

PhD Thesis, Massachusetts Institute of Technology, February 2007. (pdf) (bib)

- Scalar Operand Networks,

by Michael B Taylor, Walter Lee, Saman Amarasinghe, and Anant Agarwal.

IEEE Transactions on Parallel and Distributed Systems (Special Issue on On-chip Networks) (TPDS), February 2005.

(pdf)

(Appendix pdf) (bib)

- Deionizer: A Tool for Capturing and Embedding I/O Calls,

by Michael Bedford Taylor.

MIT-CSAIL-TR-2004-037; June 7, 2004. (pdf and ps)

- Evaluation of the Raw Microprocessor:

An Exposed-Wire-Delay Architecture for ILP and Streams

by Michael B Taylor, Walter Lee, Jason Miller, David Wentzlaff, Ian Bratt, Ben Greenwald, Henry Hoffmann, Paul Johnson, Jason Kim, James Psota, Arvind Saraf, Nathan Shnidman, Volker Strumpen, Matt Frank, Saman Amarasinghe, and Anant Agarwal.

Proceedings of the International Symposium on Computer Architecture (ISCA), June 2004. (pdf) (bib)

- Energy Characterization of a Tiled Architecture Processor with On-Chip Networks,

by Jason Sungtae Kim, Michael B Taylor, Jason Miller, and David Wentzlaff.

International Symposium on Low Power Electronics and Design (ISLPED),

August 2003.

(pdf) (bib)

- Scalar Operand Networks:

On-chip Interconnect

for ILP in Partitioned Architectures,

by Michael B Taylor, Walter Lee, Saman

Amarasinghe, and Anant Agarwal.

Proceedings of the International Symposium

on High Performance Computer Architecture (HPCA), February 2003. (pdf) (bib)

- A 16-issue multiple-program-counter microprocessor

with point-to-point scalar operand network,

by Michael B Taylor, Jason Kim, Jason Miller,

David Wentzlaff, Fae Ghodrat, Ben Greenwald, Henry Hoffman, Paul Johnson,

Walter Lee, Arvind Saraf, Nathan Shnidman, Volker Strumpen, Saman Amarasinghe,

and Anant Agarwal.

Proceedings of the IEEE International Solid-State

Circuits Conference (ISSCC), February 2003. (pdf) (bib)

- The Raw Microprocessor:

A Computational Fabric for Software Circuits and General Purpose Programs,

by Michael B Taylor, Jason Kim, Jason Miller, David Wentzlaff, Fae Ghodrat, Ben Greenwald, Henry Hoffman, Jae-Wook

Lee, Paul Johnson, Walter Lee, Albert Ma, Arvind Saraf, Mark Seneski, Nathan Shnidman, Volker Strumpen, Matt Frank, Saman Amarasinghe and Anant Agarwal.

IEEE Micro, March/April 2002. (pdf) (bib)

- The Raw processor-a scalable 32-bit fabric for embedded and general purpose computing,

by Taylor, MB and Kim, J and Miller, J and Ghodrat, F and Greenwald, B and Johnson, P and Lee, W and Ma, A and Shnidman, N and Strumpen, V et al.

Hot Chips XIII, August 2001. (bib)

- Baring it all to Software: Raw Machines,

by Elliot Waingold, Michael Taylor, Devabhaktuni

Srikrishna, Vivek Sarkar, Walter Lee, Victor Lee, Jang Kim, Matthew Frank,

Peter Finch, Rajeev Barua, Jonathan Babb, Saman Amarasinghe, and Anant

Agarwal.

IEEE Computer, September 1997, pp. 86-93.

(pdf) (bib)

- The Raw Compiler Project,

by Anant Agarwal, Saman Amarasinghe, Rajeev Barua,

Matthew Frank, Walter Lee, Vivek Sarkar, Devabhaktuni Srikrishna, and Michael

Taylor.

Proceedings of the Second SUIF Compiler Workshop,

Stanford, CA, August 21-23, 1997.

(pdf) (bib)

- The RAW Benchmark Suite: Computation Structures

for General Purpose Computing

,

by Jonathan Babb, Matthew Frank, Victor Lee,

Elliot Waingold, Rajeev Barua, Michael Taylor, Jang Kim, Srikrishna Devabhaktuni,

and Anant Agarwal.

IEEE Symposium on Field-Programmable Custom

Computing Machines (FCCM), Napa Valley, CA, April 1997. (pdf) (bib)

-

The Raw Specification

by Michael B Taylor.

Final Version (5.02). December 2005.

(pdf)

|

by Apr 2.

by Apr 2.